電圧負帰還(NFB)を全く掛けないプリメインアンプ(インテグレーテッドアンプ)の初段をSRPP化してみようと思い、そのひとつが完成しました。

SRPPは入力によって電流が変化する抵抗負荷回路に対して、電流が変化しない定電流負荷回路であると言われています。

電流が変化する抵抗負荷より、電流が変化しないSRPPの方が良い音がするのではないかとも言われています。

そこで、ひとつの研究テーマと捉え、挑戦してみました。

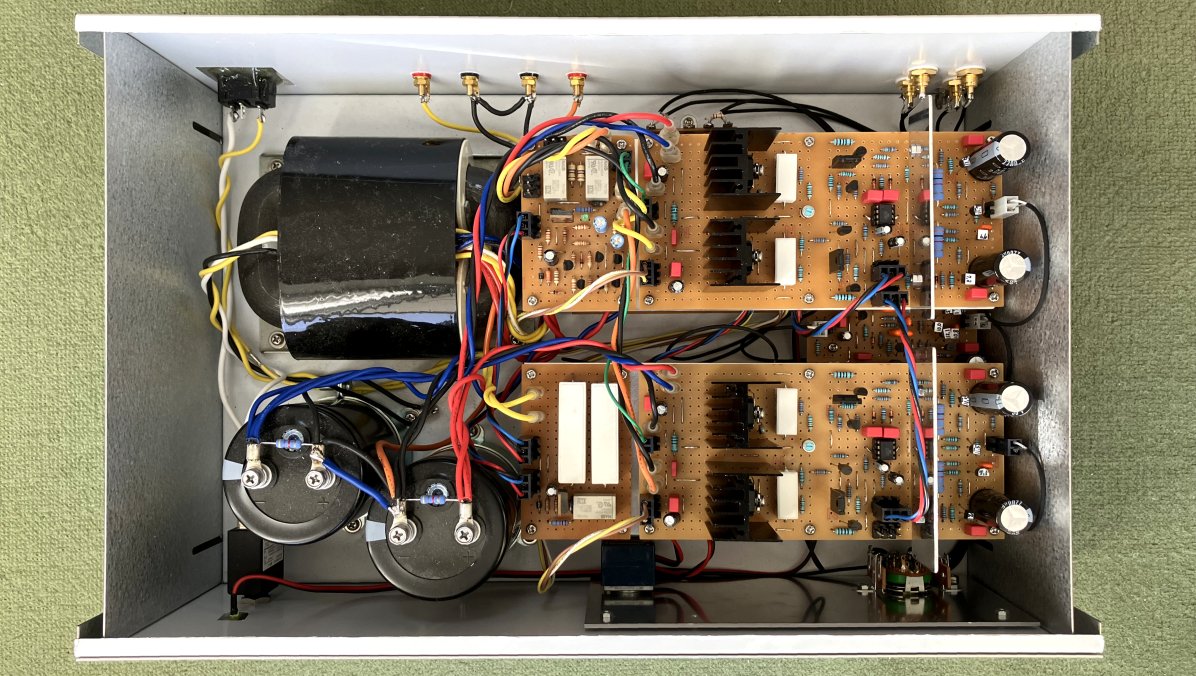

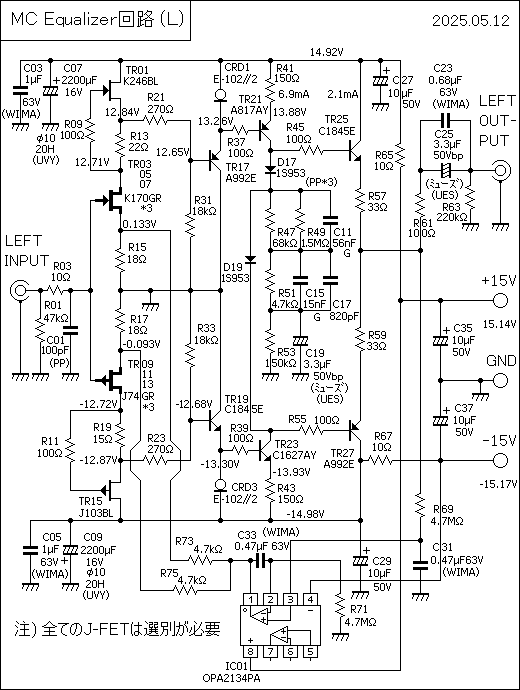

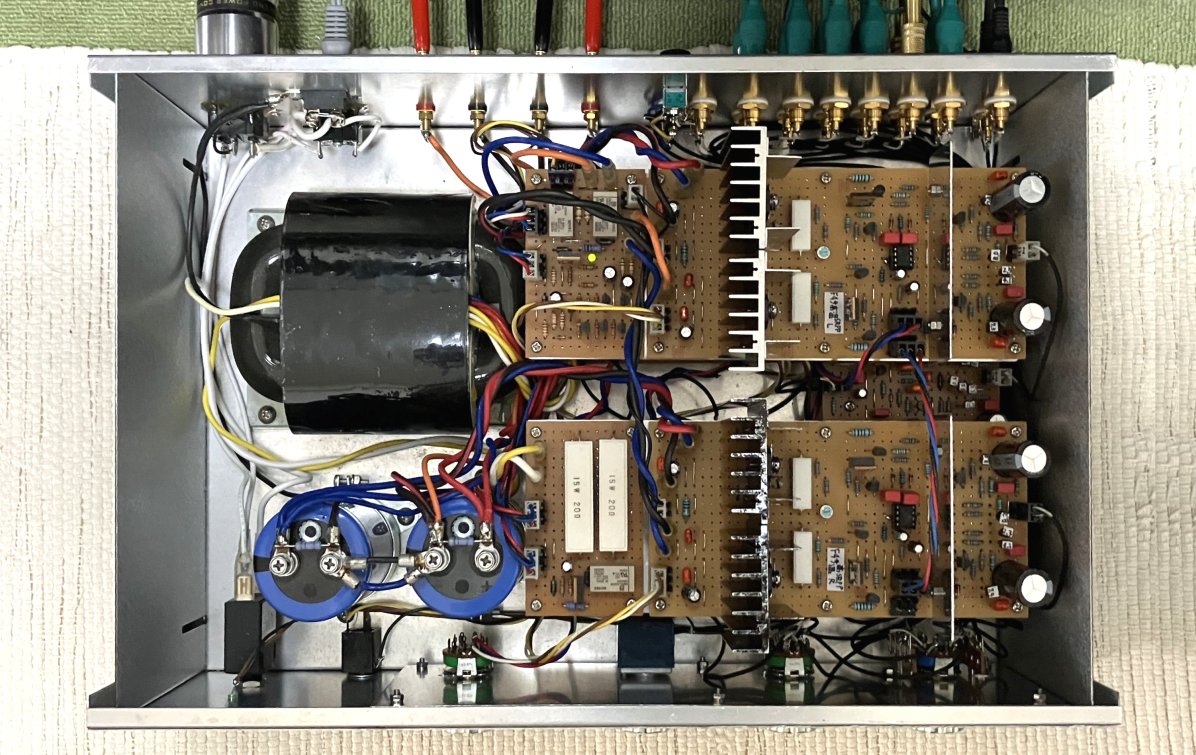

冒頭の写真は増幅初段をSRPPにした初段FE型プリメインアンプを搭載した1号機内部の上部写真です。

メインアンプは通常のラインアンプとメインアンプを統合した高利得メインアンプになりました。

セットの右半分(前方中央のメインボリューム位置より右側)が初段FE型SRPP高利得メインアンプです。

部品点数がさらに増える全TR型(全バイポーラーTR型)用のスペースと放熱器をさらに大きくする為のスペースを考慮したのでAT-1Wと言う実験基板を丸々使う事にしました。

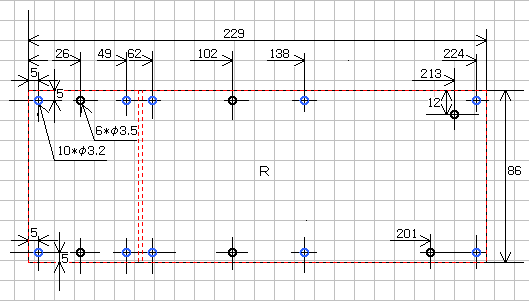

プロテクター回路基板、突入電流緩和回路基板は変更ありませんが、上部基板の載る上下分離用シールド板2枚は変更しました。

上下分離用シールド板の図面は最後に紹介します。

セットの下部にはMC-EQ基板とラインアンプの代わりの基板、および電源基板があります。

以下、SRPP化した各回路について紹介します。

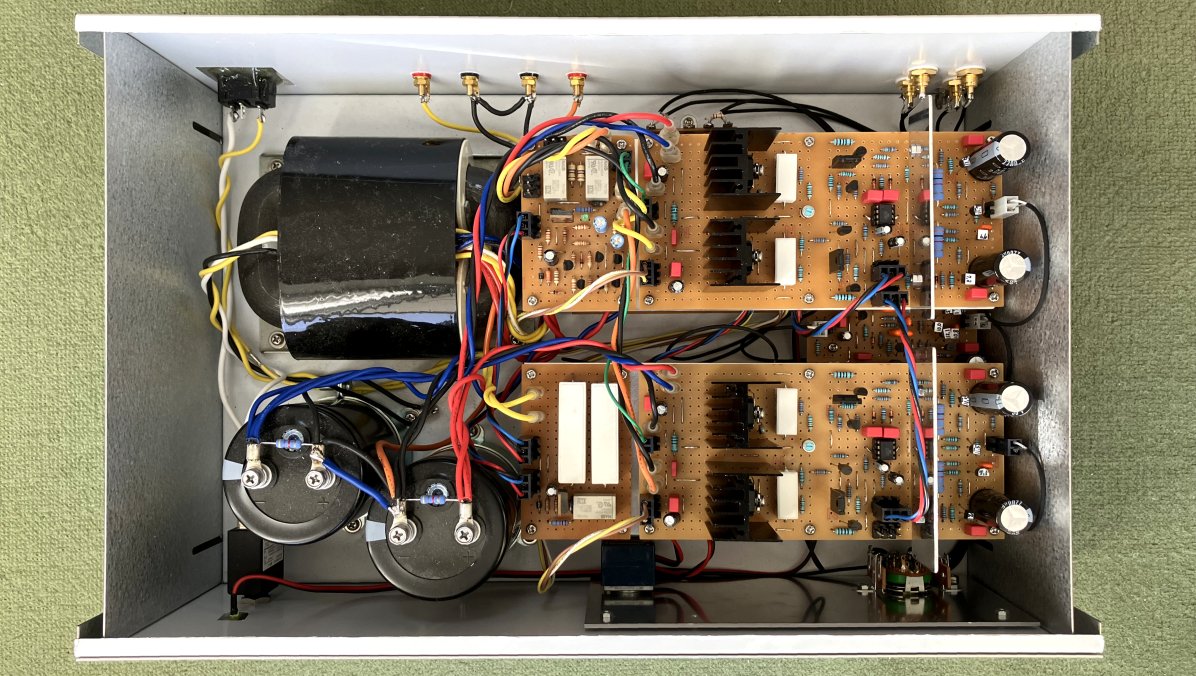

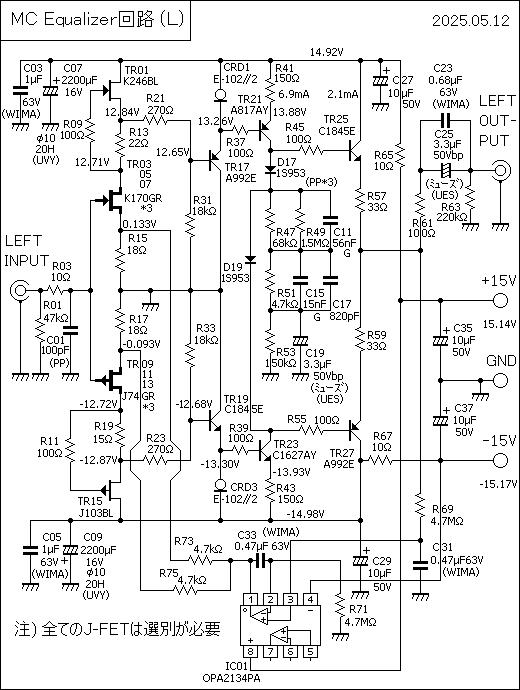

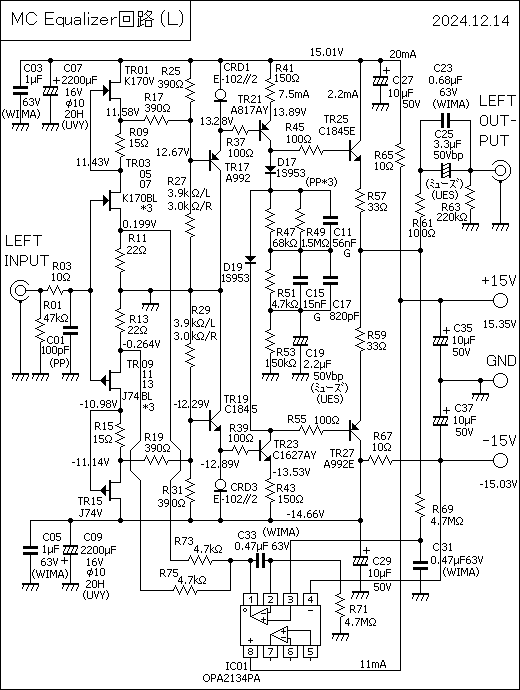

1.MC-EQ回路

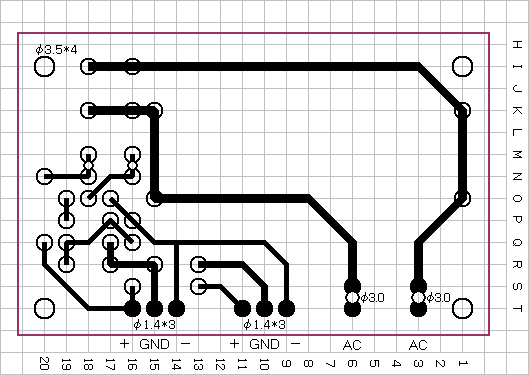

①.回路図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

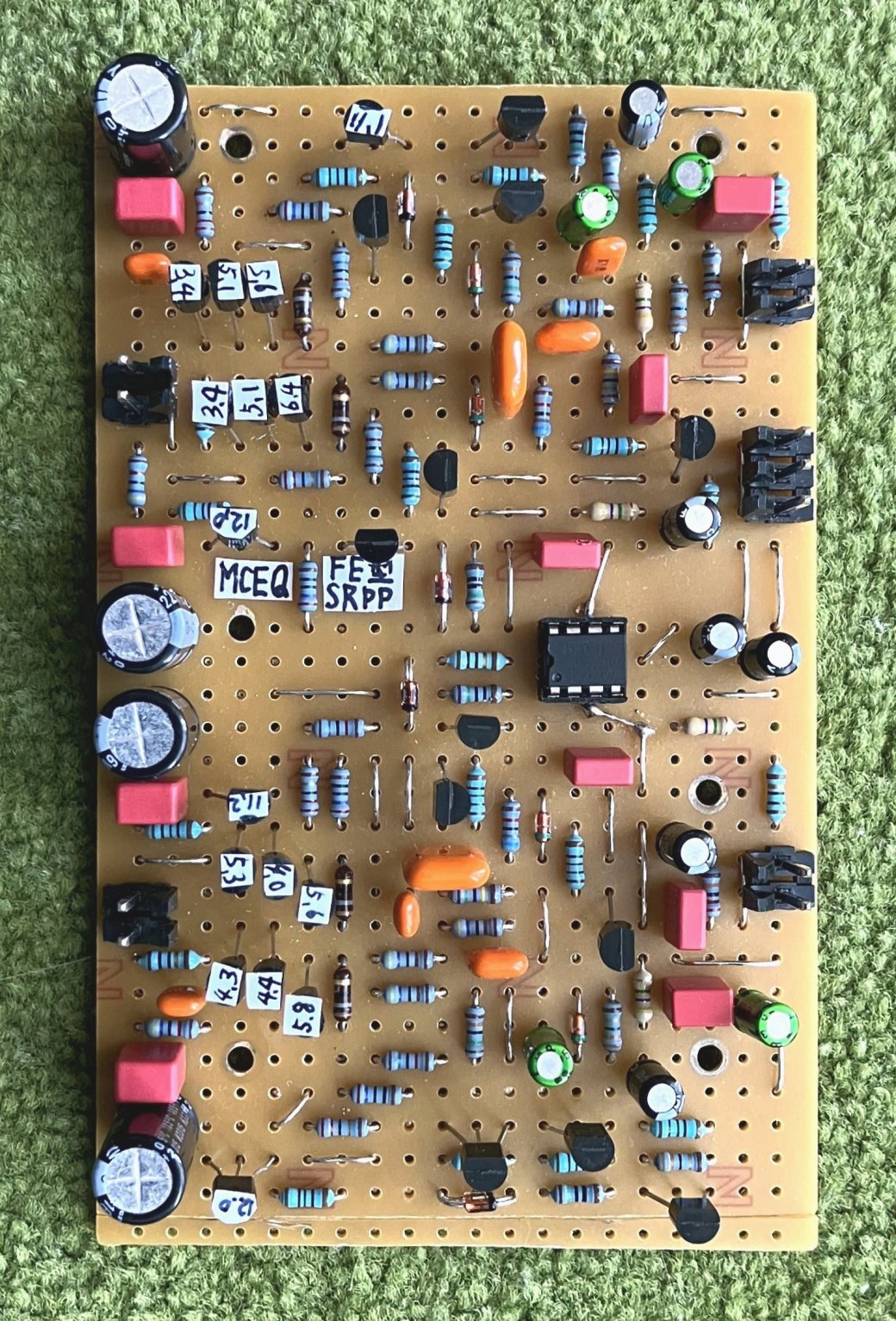

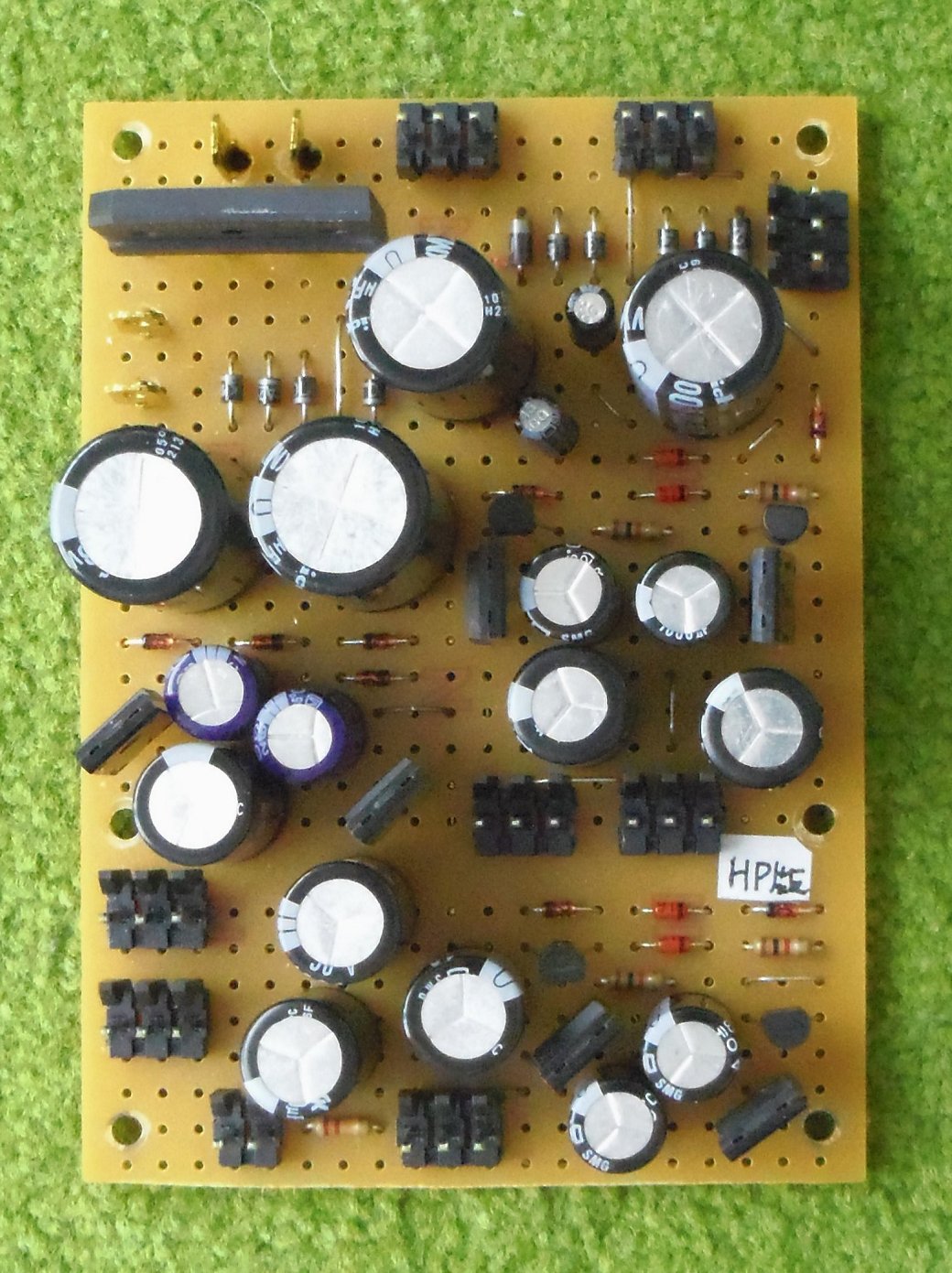

②.プリント基板部品面写真

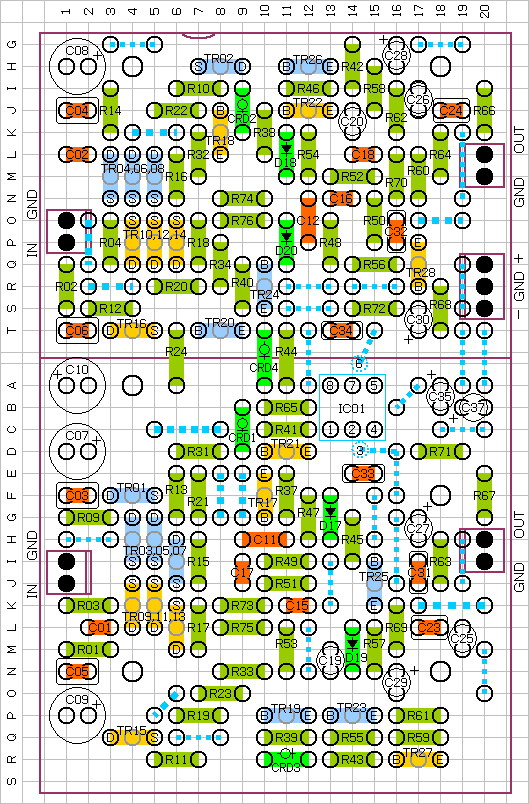

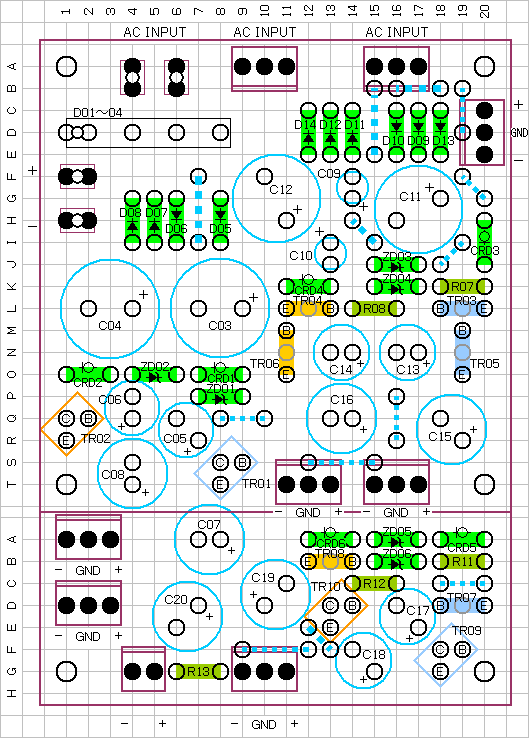

③.プリント基板部品面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

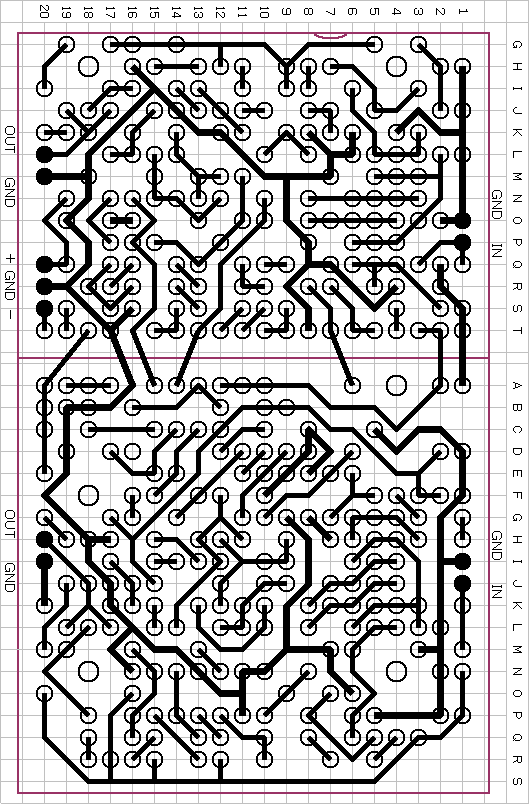

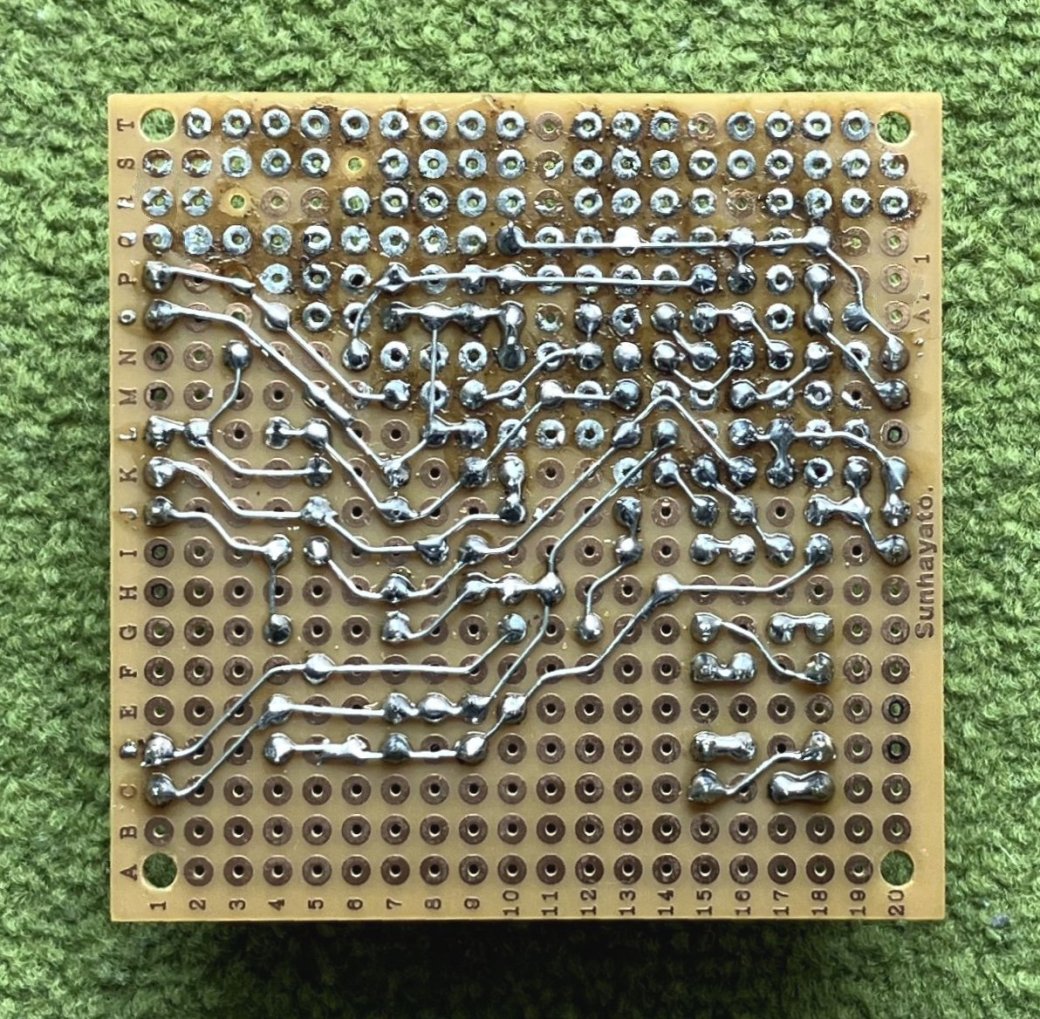

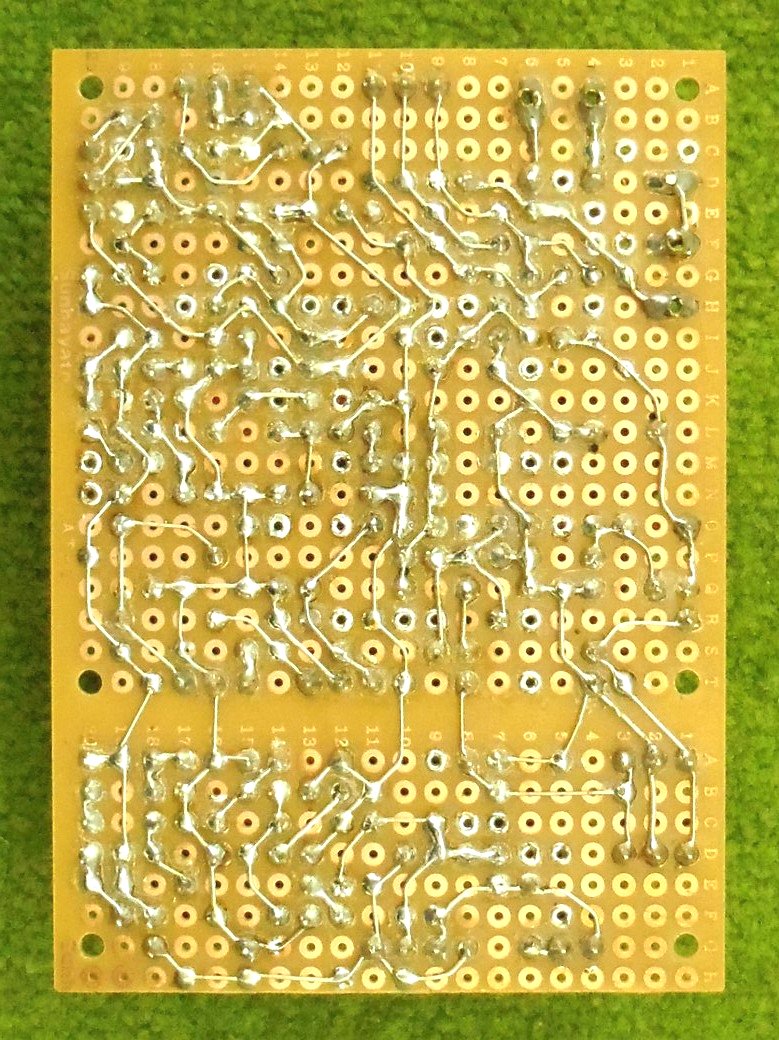

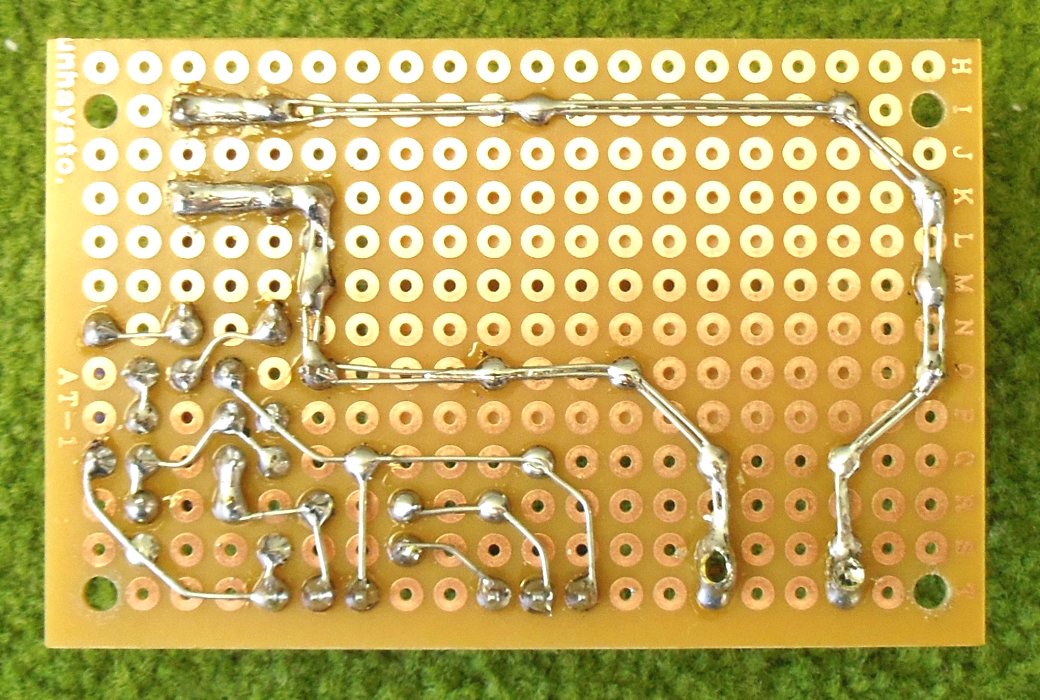

④.プリント基板銅箔面写真

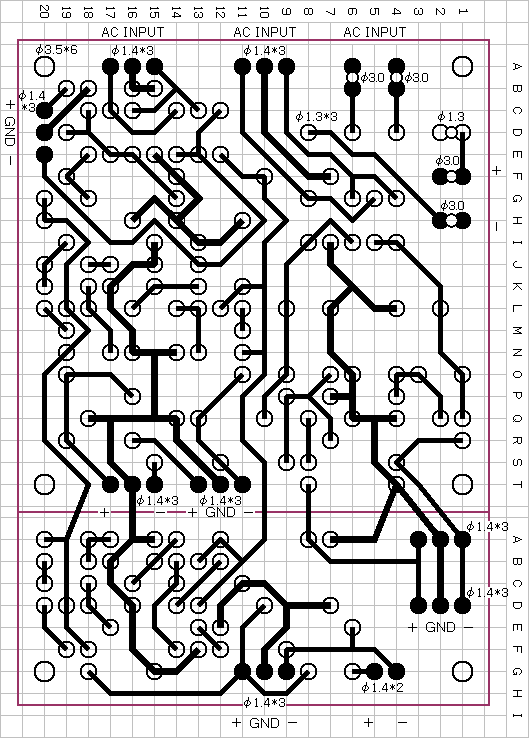

⑤.プリント基板銅箔面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

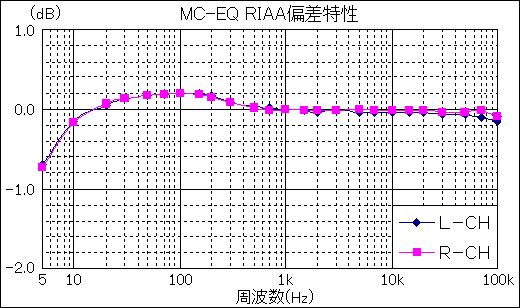

⑥.RIAA偏差特性

⑦.出力電圧対歪率特性

☆.説明

筆者は真空管回路でSRPP回路の設計をした経験がありますので、その経験に基づいて設計を開始しました。

しかし、半導体はJ-FETでも真空管より遥かに利得が高く、加えていわゆるSRPP段は増幅段のドレインからSRPP段のゲートに信号を加え、これがソースに出力しますが、増幅段のドレインはSRPP段のソースと自己バイアス分の違いしかなく、ゲートとソースは同位相である事から正帰還である事が分かりました。

つまり、SRPPは同相増幅器なのです。

そこで第1試作では増幅段に使用した高利得素子と同じ素子をSRPP段に使用しましたが、これを改め、SRPP段には利得の低い素子(品番)を使う事にしました。

さらに、MC-EQでは初段を3パラにしてノイズ低減を図りますが、SRPP段はシングルにしますのでドレイン電流が3倍流れます。

この事を考慮して、増幅段のIDSS、SRPP段のIDSSを決めました。

これは真空管でMCヘッドアンプを設計した時に、2パラの増幅段とシングルのSRPP段の品種を変えて対応したのと同じです。

この事により、過剰利得が抑制され、MCダイレクトEQの利得60dB/1kHzを維持しながらSRPP化する事が出来ました。

なお、中段のエミッターフォロアーは定電流ダイオードを使用して、この部分も定電流化しました。

定電流ダイオードは素子の特性に鑑み1mAのものを2本並列にしますが、1つの穴に2本入れています。

回路設計基板設計を進めていく中で、基板寸法を大きくしなければならなくなり、前写真のような延長をしました。

2.ラインアンプの代わりの回路

回路検討中に初段をSRPP型にすると利得が高くなり過ぎて、利得が20dB前後のラインアンプやメインアンプはSRPPを生かした回路がほとんど設計不可能と考えられました。

その為、ラインアンプとメインアンプを統合して高利得メインアンプにする事にしました。

しかし、回路配置上の都合によりメインボリュームと高利得メインアンプの入力が離れていました。

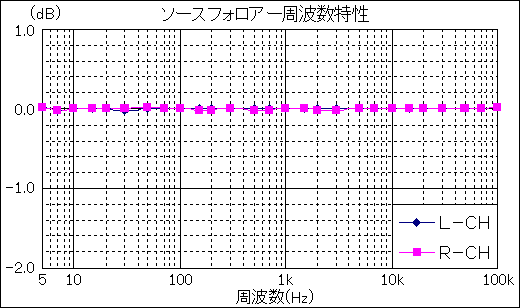

対策として、コンプリメンタリーのソースフォロアーを入れたのですが、2025年12月に改善すべき点が見つかったのです。

下記は改善後のものです。

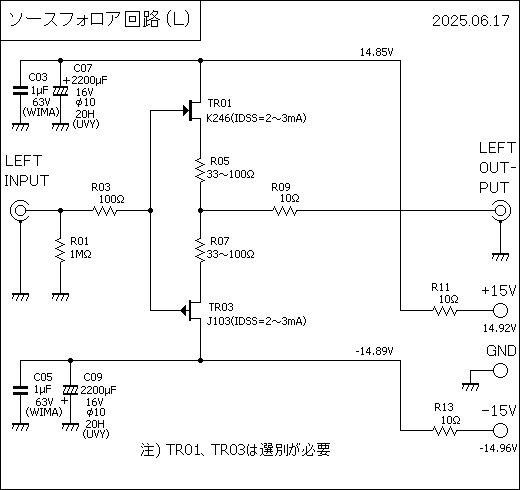

①.回路図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

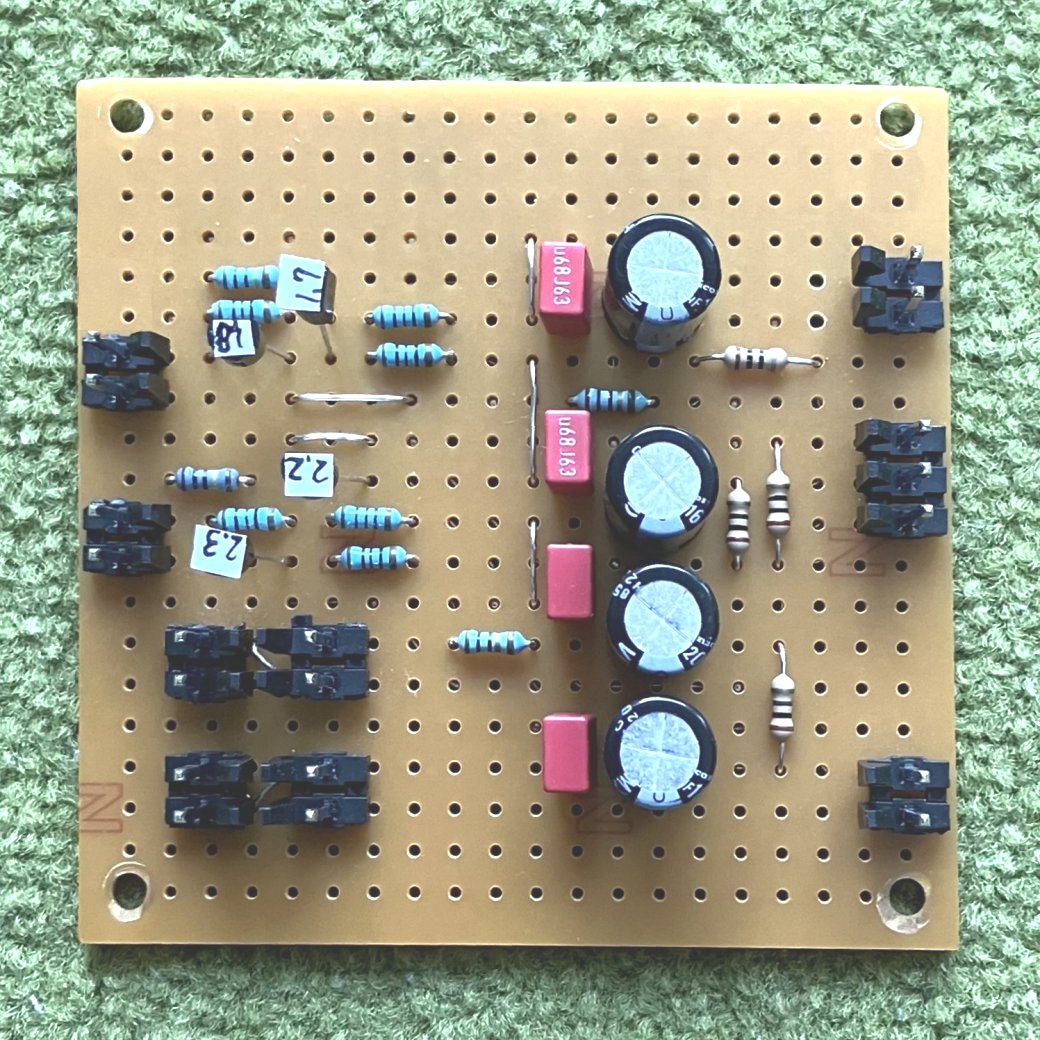

②.プリント基板部品面写真

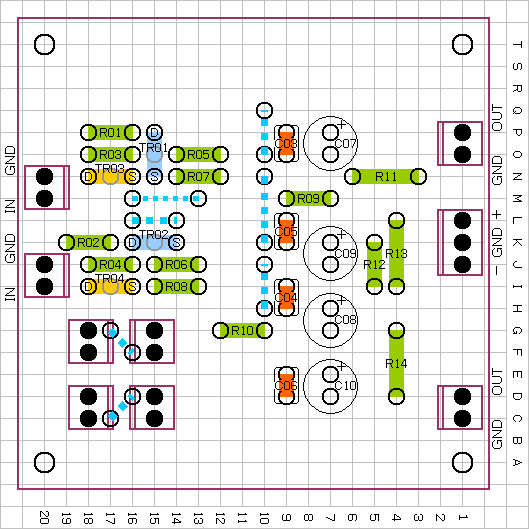

③.プリント基板部品面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

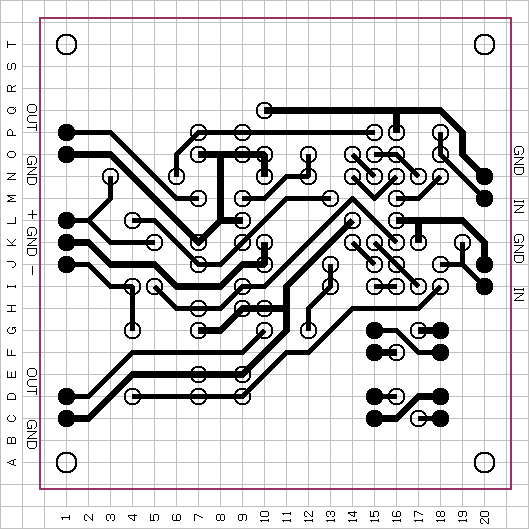

④.プリント基板銅箔面写真

⑤.プリント基板銅箔面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

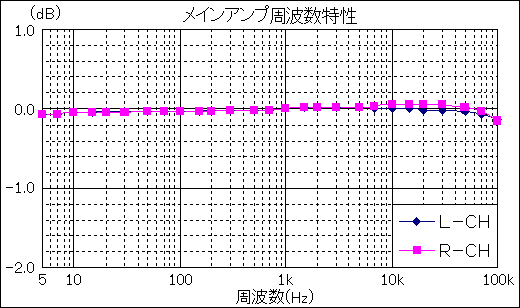

⑥.周波数特性

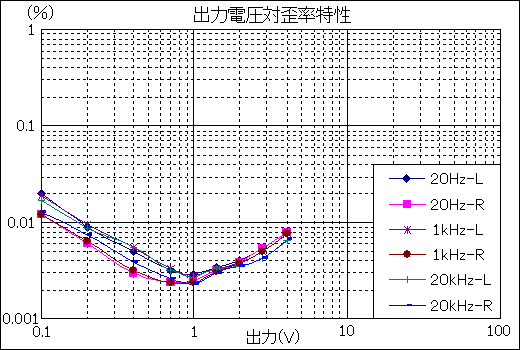

⑦.出力電圧対歪率特性

他の歪率特性図より、歪率の値が1桁低いので、ご注意ください。

☆.説明

P-CHのIDSSをN-CHのIDSSより0.2mA程度大きくした方が、出力のDC電圧がゼロVに近づくようです。

更なる調節は両-CHのソース抵抗を加減するか半固定抵抗にしてください。

もし、マルチアンプを作る場合は、この出力の後にチャンネルディバイダーを入れ、メインアンプを高利得型にしてください。

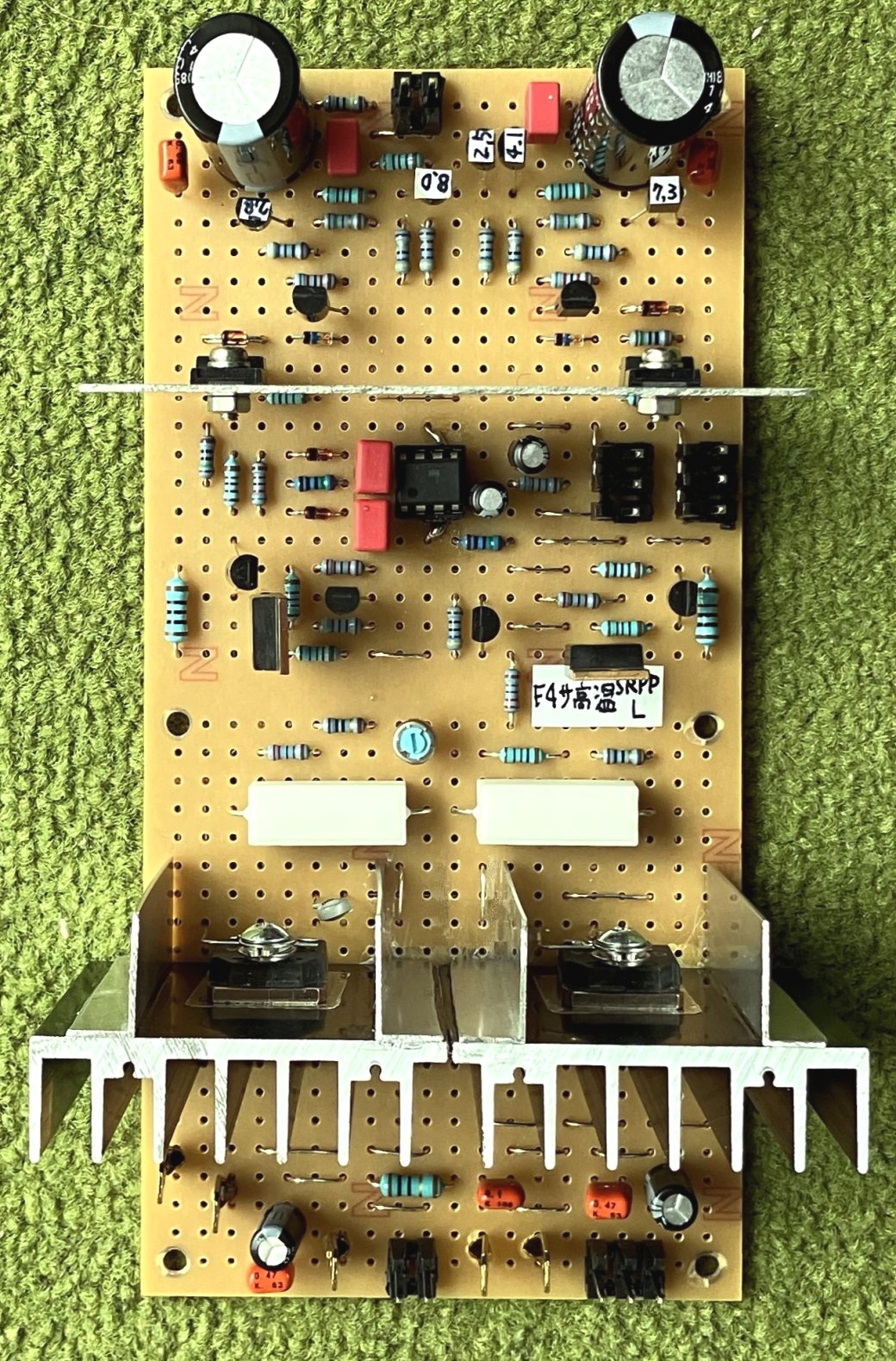

3.高利得ダーリントン4段型メインアンプ

パワーTRとして2SA1386Aと2SC3519AのPランクまたはYランクを使ってきましたが、通常店舗では入手が不可能となり、代替を探したところ、2SA1294と2SC3263のYランクが入手可能と分かりました。

メーカーは同じサンケン電気で、hfe以外の特性は同等のようです。

また、デジタルテスターでhfeを測定し、差が10以内で組み合せましたところ下記のデータを得ました。

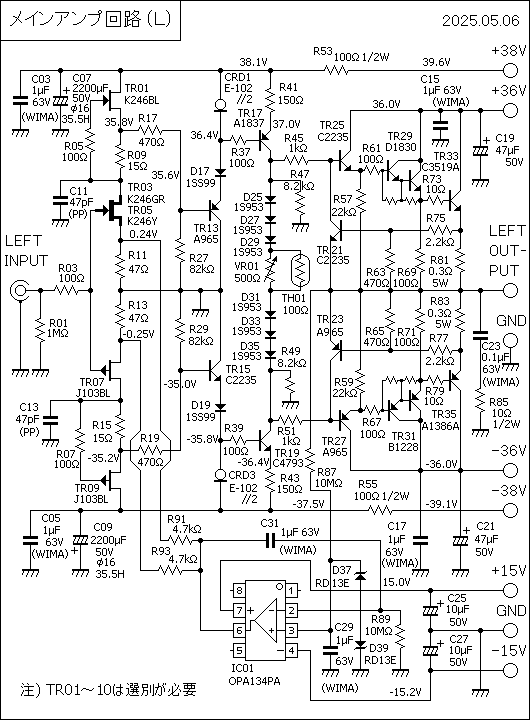

①.回路図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

②.プリント基板部品面写真

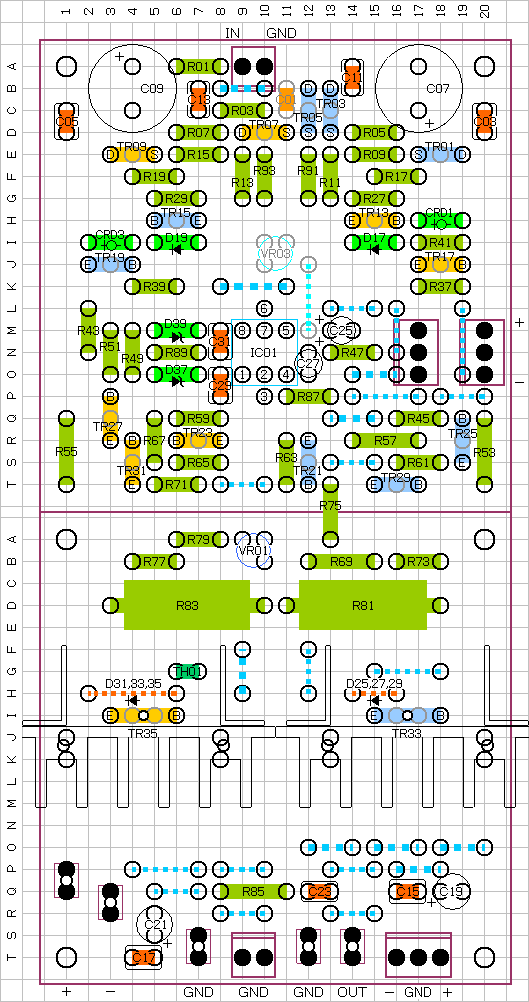

③.プリント基板部品面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

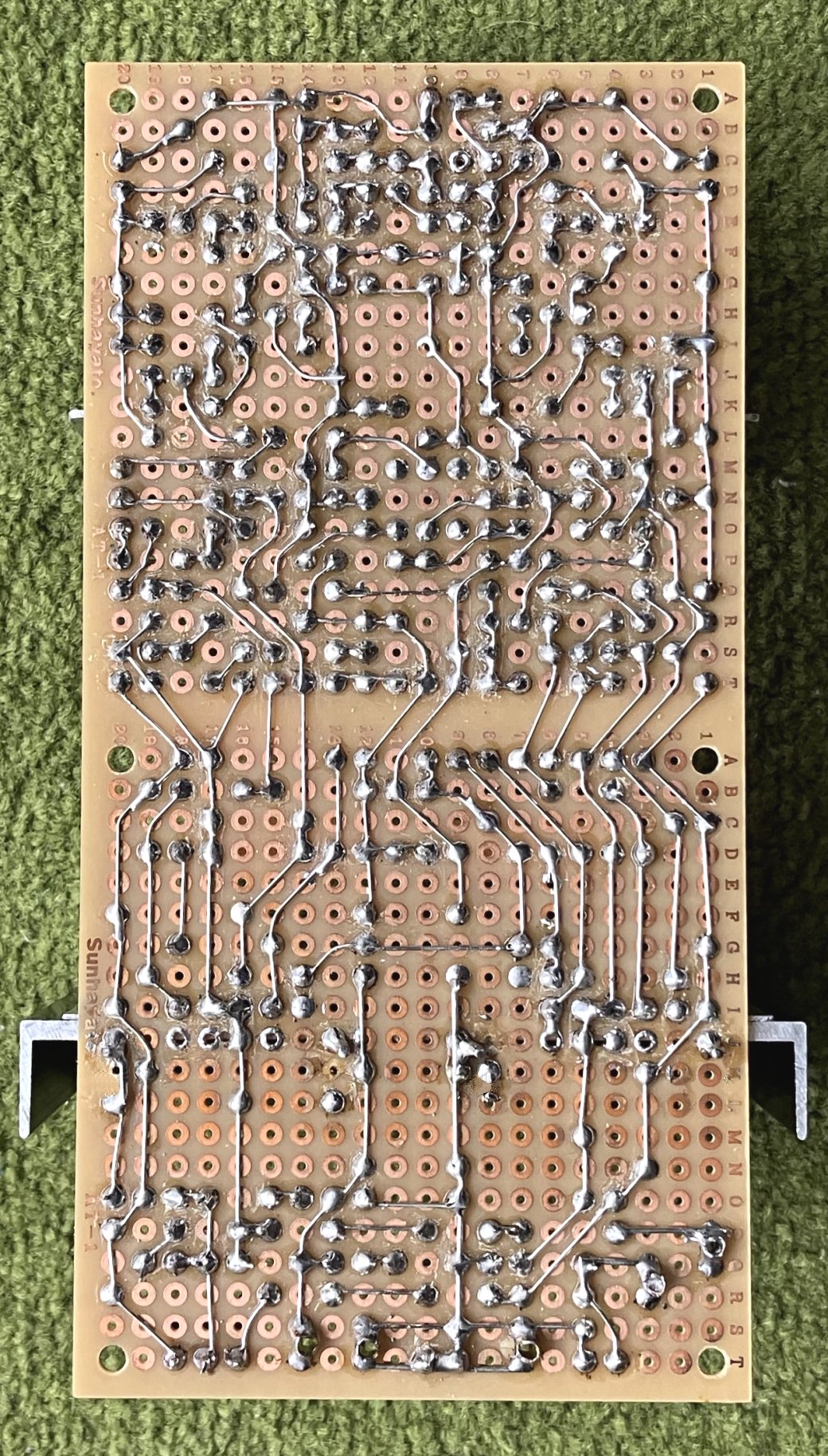

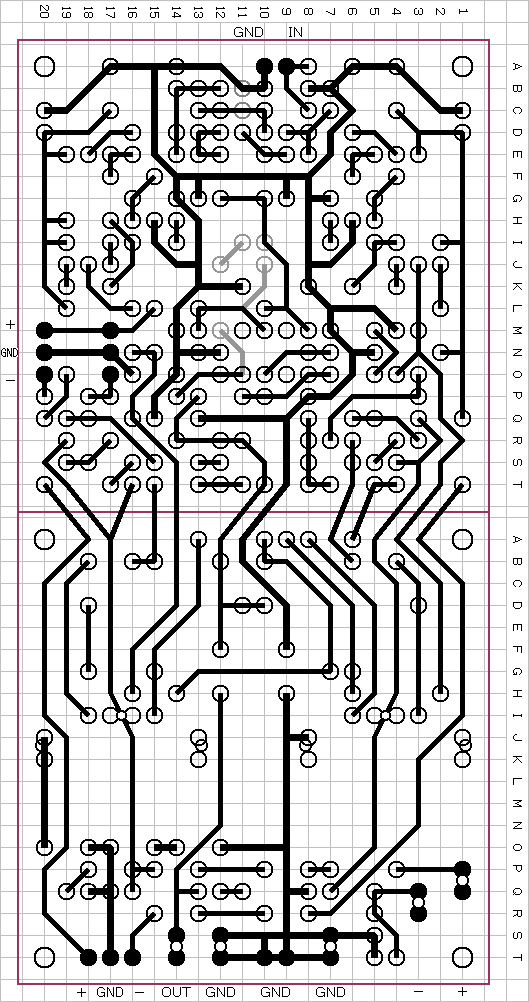

④.プリント基板銅箔面写真

⑤.プリント基板銅箔面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

⑥.周波数特性

⑦.出力電力対歪率特性

☆.説明

第1試作では通常利得で設計をしましたが、SRPPによる過剰利得を抵抗追加で抑えた為に、抵抗負荷に近い音質になりました。

しかし、MC-EQのように低利得素子に置き換える事が出来ないので、ラインアンプと統合する高利得メインアンプにする事にしました。

ところで、抵抗負荷の初段FE型高利得メインアンプを作った事があるのですが、ラインアンプの出力に付けるカップリングコンデンサーがなくなってしまった事から、真につまらない音になってしまい、お蔵に入れたのです。

この点で、SRPPならどうだろうかと考えたのですが、他の方法も思い浮かばなかったので、高利得型で取り組む事にしました。

初段FETのIDSSを色々と組み合せて行く中でN-CHのFETを2パラ、P-CHのFETをシングルにしたところ、今までにない低歪率が実現しました。

前出のデータの通りですが、例え小出力の部分だけとは言え、無帰還のメインアンプでバラツキによっては0.1%を切るような低歪率は見た事がないのではないでしょうか。

これなら意味のあるアンプになったのではないかと考え、試聴もしましたが、存在意義のある音になったと思います。

また、当試作では、放熱器の変更による、温度上昇の改善をしていまして、今回はその第1試作です。

定格の1/8出力と言う規定の測定方法で、約110℃から約95℃になりました。

次の試作、全TR型SRPPにおいて更なる改善をしたいと考えています。

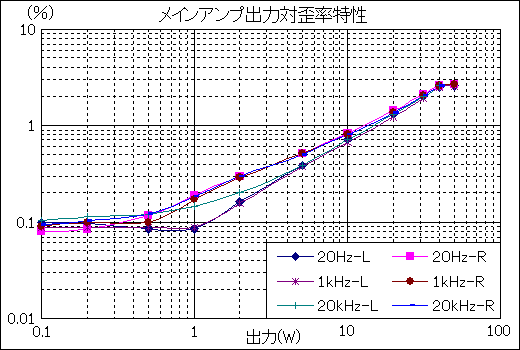

4.電源回路

機器全体に電源を供給します。前テーマ用と同じです。

特徴としては、アイドリング電流の安定化の為にメインアンプの増幅段用の電源を安定化電源にした事、プリアンプ用の電源のリップルを極限まで減らす工夫をしている事です。

①.回路図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

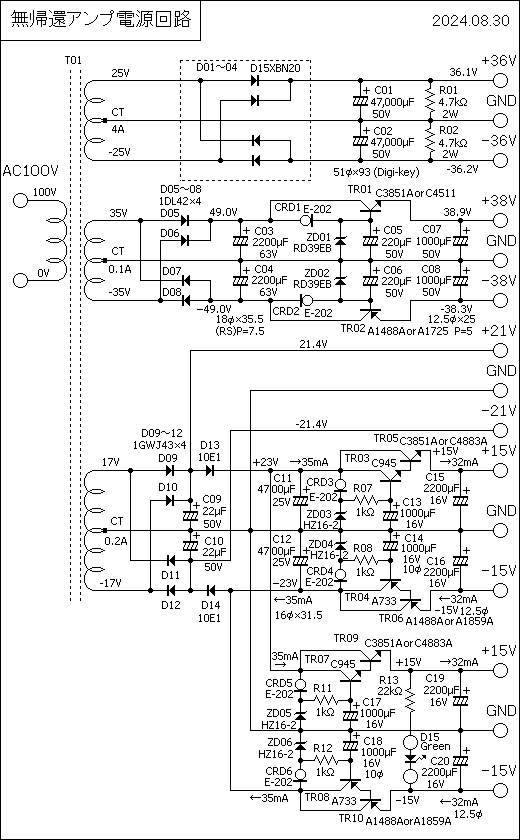

②.プリント基板部品面写真

③.プリント基板部品面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

④.プリント基板銅箔面写真

⑤.プリント基板銅箔面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

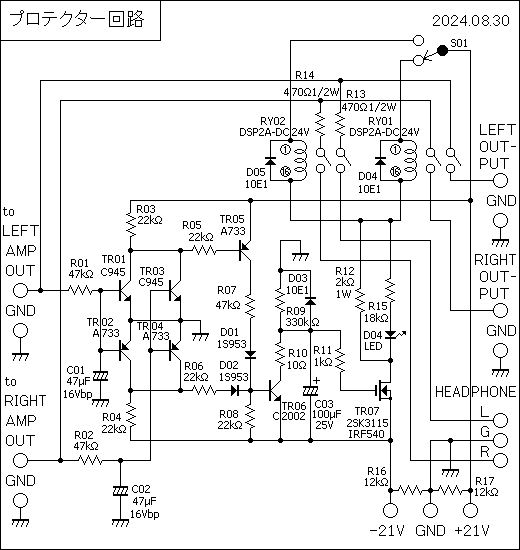

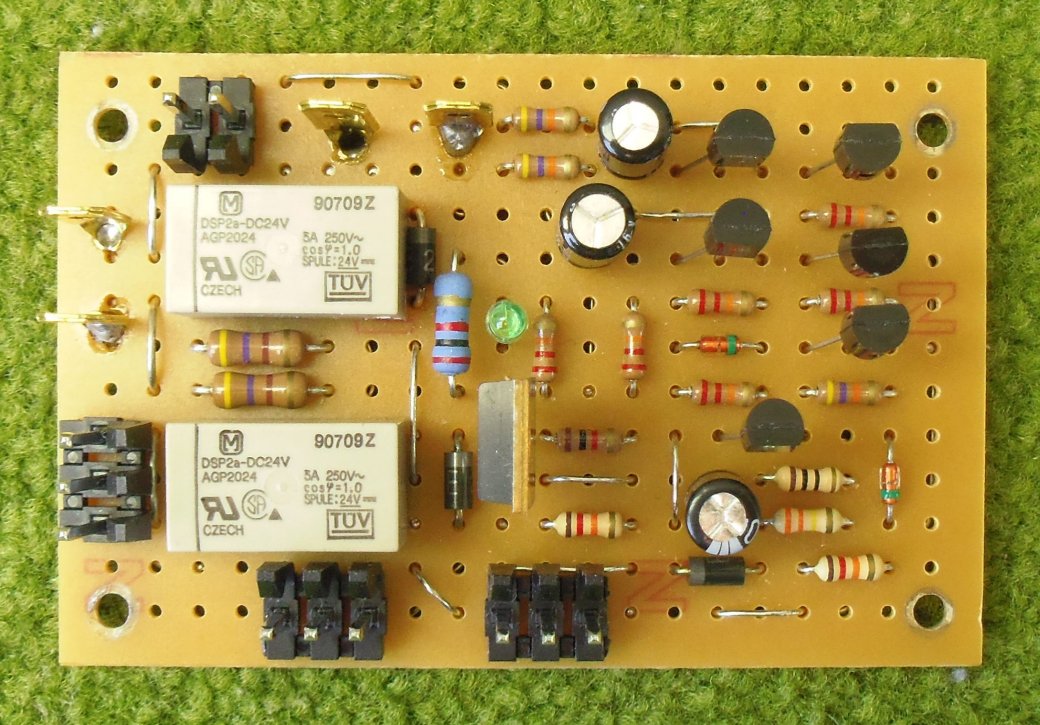

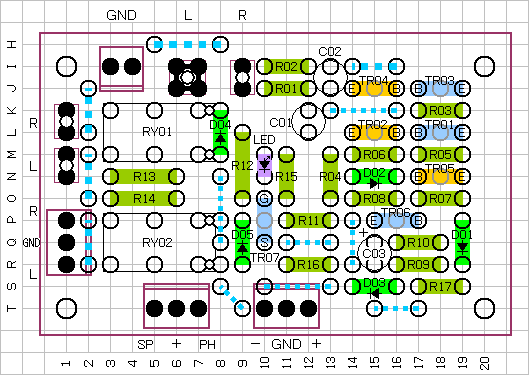

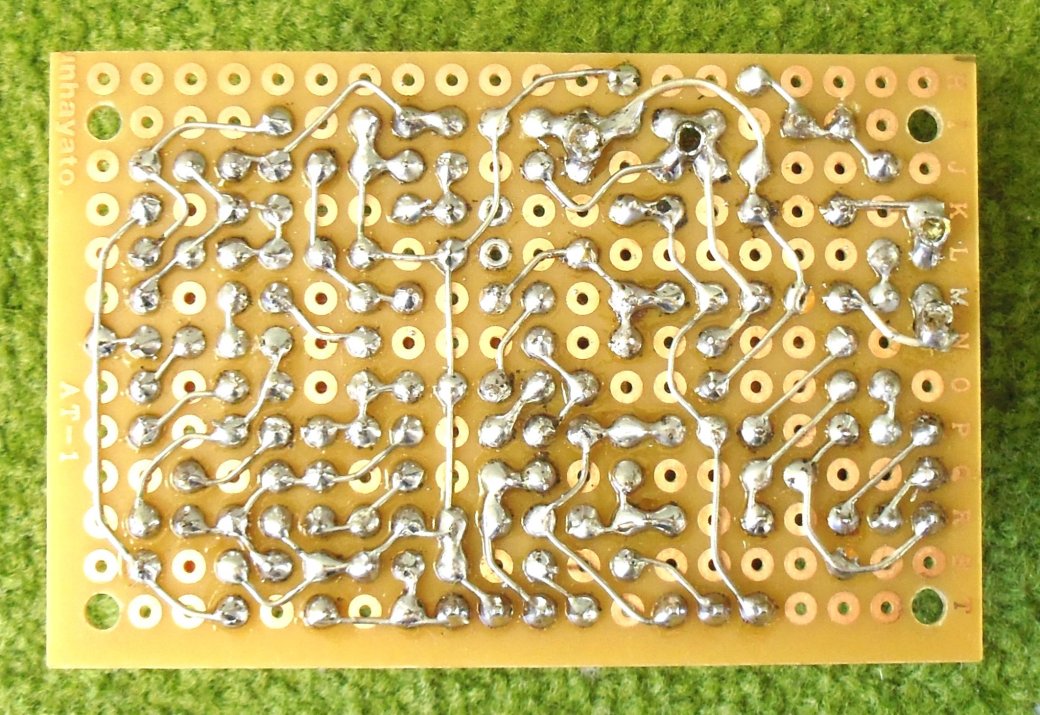

5.プロテクター回路

メインアンプの出力がDC±600mV以上になった時に出力を開放します。

筆者が昔から使っている回路ですが、入力時定数とTRを見直しました。

①.回路図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

②.プリント基板部品面写真

③.プリント基板部品面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

④.プリント基板銅箔面写真

⑤.プリント基板銅箔面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

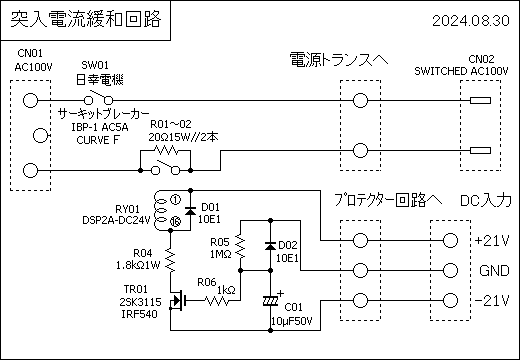

6.突入電流緩和回路

電源トランスの1次側巻線抵抗が約1Ωなので、電源スイッチON時の突入電流が約100Aになります。

これを約10Aに抑え、約2秒後に全電圧がかかるようにする為の遅延回路です。

①.回路図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

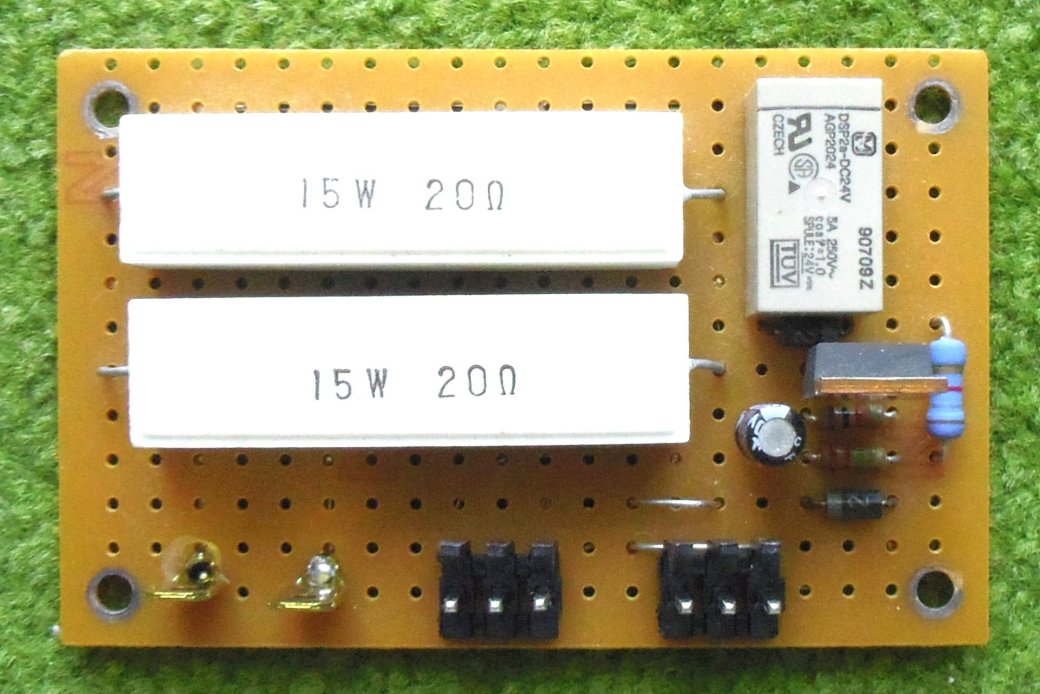

②.プリント基板部品面写真

③.プリント基板部品面図

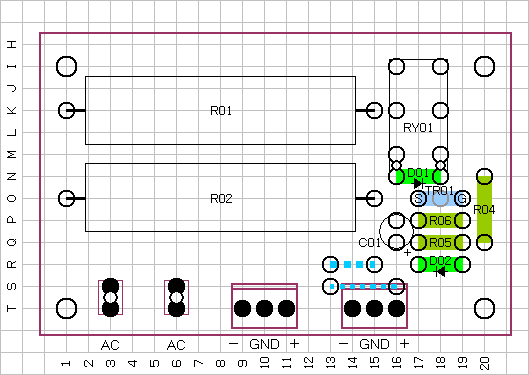

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

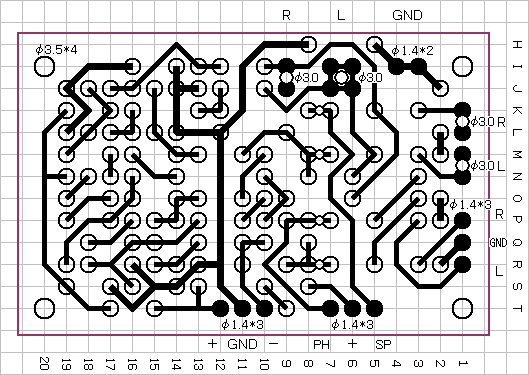

④.プリント基板銅箔面写真

⑤.プリント基板銅箔面図

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

7.全体回路図

回路が膨大な為、プリアンプ他とメインアンプ他の2つに分けました。

さらにA4に印刷する場合、印刷倍率100%で端が欠ないようにしましたが、もし、欠ける場合はフチなし全面印刷とか印刷倍率の低減を適宜採用してください。

①.初段FE型SRPPプリアンプ他

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

②.初段FE型SRPPメインアンプ他

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

8.上下分離用シールド板

L-CH用とR-CH用の2枚で、板厚は各々2mmです。

①.L-CH用

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

②.R-CH用

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

9.試聴

これが半導体のSRPPの音か、そう言う音が出たのではないかと思います。

以上

このページのトップへ戻りたい方はここをクリックして下さい。

トップページ(目次)へ戻りたい方はここをクリックして下さい。