2005年初頭〜2007年前半、X'tal発振を分周して作った400kHzをクロック(CLK)とした独自回路による全域型D級アンプを開発しましたが、今般それの改良に取り組みました。

また、当初の設計はクルマ用(バッテリー電源、4Ω負荷)だったのですが、最終的には家庭用(AC100V電源、8Ω負荷)にすることにしました。

☆.ページトップの写真は家庭用として出来上がったアンプの正面写真です。

ただし、販売用ではありませんので入力切替のようなものは付いておりません。

以下、順を追って説明します。

☆.第1段階

最初はアナログプリアンプ段のICをNE5532からOPA2134UAに変更とか、コンパレータをLM360からLM319D(NJM319D)に変える事を主な変更点として、周波数特性、歪率、音質についての追及をしました。

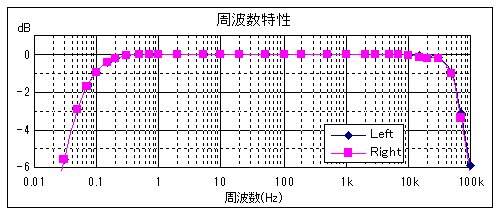

この時得られた特性ですが、先ず周波数特性を示します。

低域は理論特性、高域は実測で50kHzでは約−1dBです。

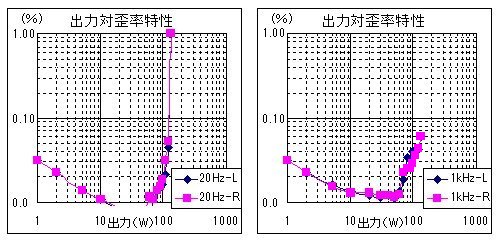

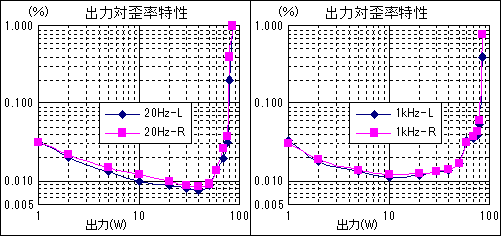

次のグラフは20Hzと1kHzの歪率です。

20Hzの最低歪率は約0.009%、1kHzの最低歪率は約0.017%です。

☆.試聴テスト

試聴テストは研究所本拠(自宅)のオーディオセットで行いました。

低域については上の特性図のようにA−10Ⅳ(改2)と同じカットオフ周波数=0.05Hzで満足できる音質になりました。

スピーカーの低域共振周波数の影響が完全に排除され、質的に確かな低音になりました。

次に高域ですが、何か物足りないものを感じました。

SACDのバイオリンの音やトライアングルの音が量的質的に物足りないのです。

☆.第2段階

目標は高域の改善ですが、その手法については事前検討を重ねた結果、CLKを1MHzにすることにしました。

X'tal発振による完全固定の1MHzです。

そして、1MHzを生かすICやMOSFETの選択と周辺定数の検討をしました。

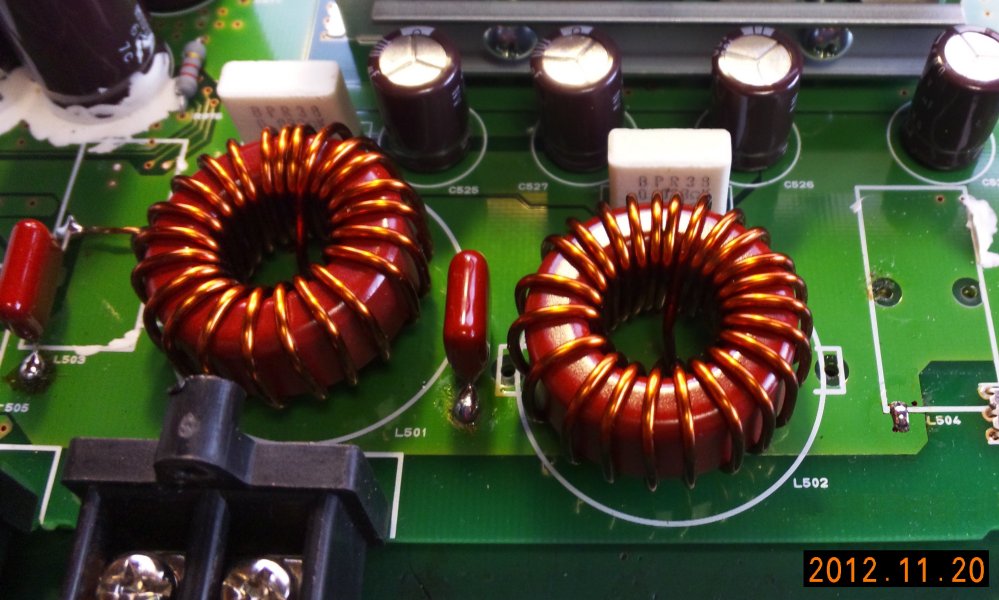

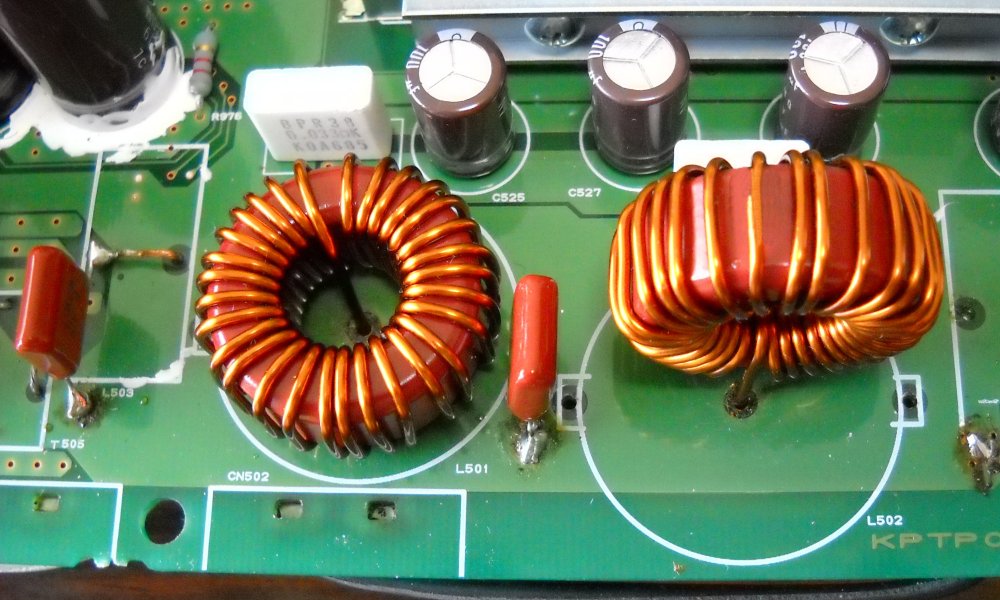

アンプ出力に入れるLPFのコイルは7.2μHという小容量で済むようになりました。Cは0.22μF

その写真を次に示します。

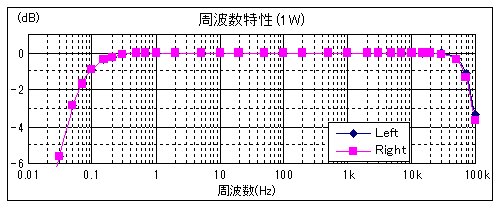

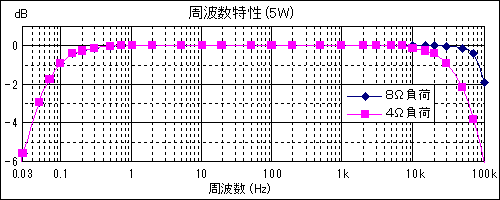

次に周波数特性を示します。

低域は理論特性、高域は1W=0dBの実測で50kHzでは約−0.3dBです。

CLKの漏れが400kHzの時より22dB減ったので1Wで測れるようになりました。

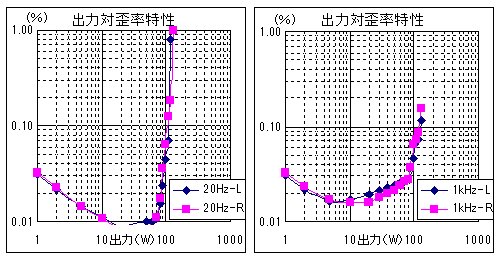

次のグラフは20Hzと1kHzの歪率です。

20Hzの最低歪率は約0.008%、1kHzの最低歪率は約0.012%でとなりCLK=400kHzより良くなりました。

☆.試聴テスト

再び本拠にて試聴テストをしました。

結果ですが、いわゆるD級らしい音というものから脱却しました。

☆.第3段階

最後に電源をAC100Vにし、指定負荷抵抗を8Ωにすることにしました。

元のアンプの中には自動車運転中の電源電圧DC14.4Vから100W×2CHを出すためにスイッチング電源を積んでいますが、それをAC100Vを直接整流したDC約130Vを入力とするように変更しました。

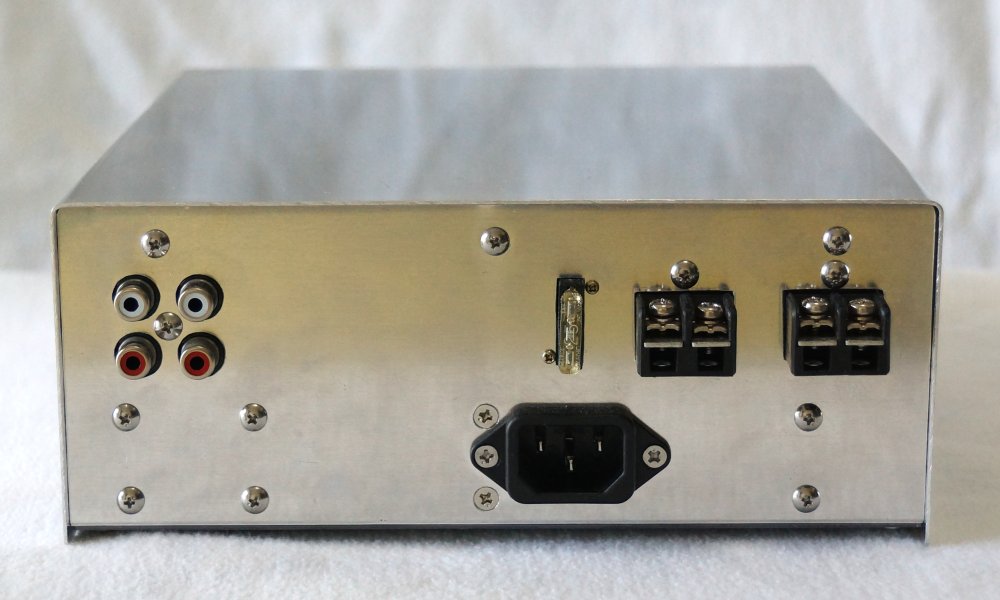

また、電源スイッチとボリュームを前面パネルにつけ、出力端子は背面パネルに移動して家庭用のスタイルにしました。

次に背面パネルの写真を掲載します。

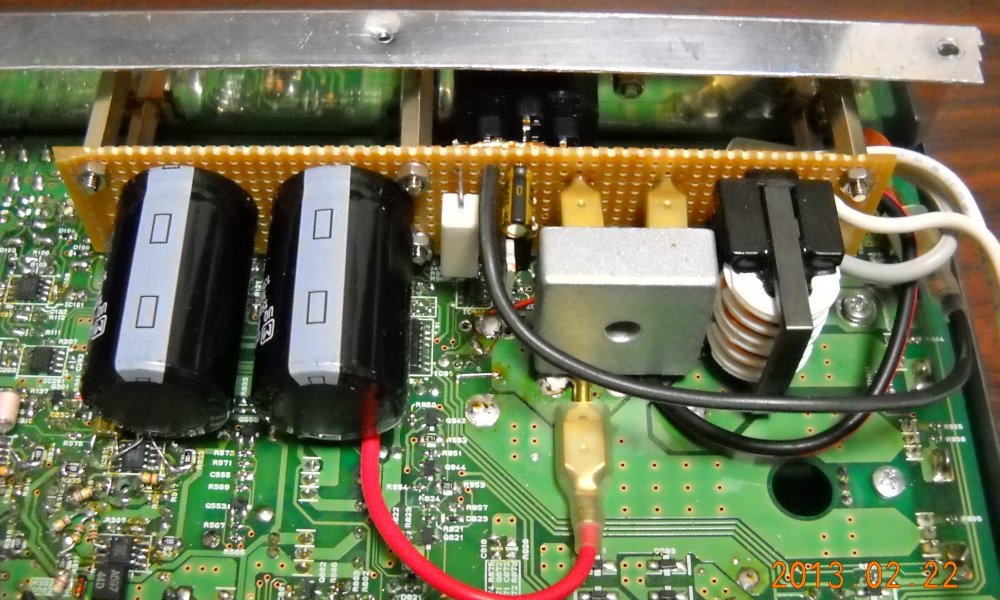

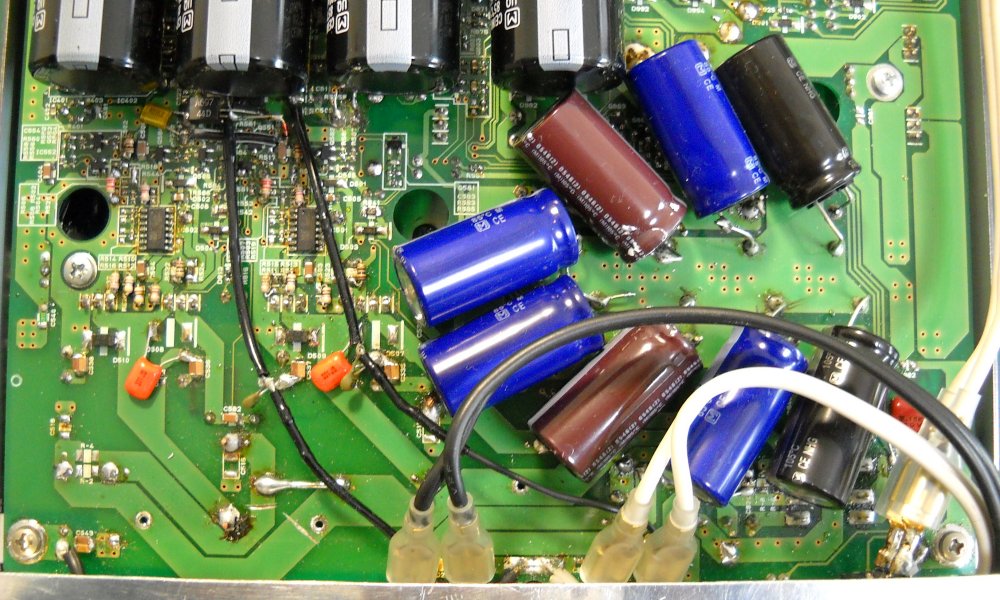

次に背面パネルの裏側に追加したAC100Vの整流平滑部分の当初の写真を掲載します。

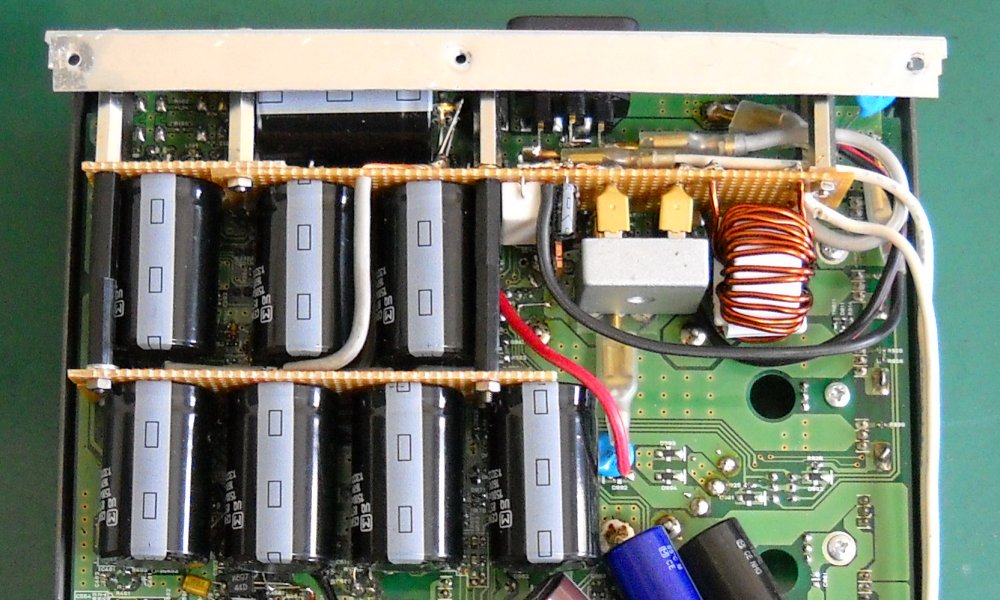

しかし、重低音が全く出ず、それを出そうとしてコモンモードフィルタを外すと高域が濁るという事で、結果として次の写真のようになりました。

1次側の平滑コンデンサは12,000μF、写真の右上にある1次のコモンモードノイズフィルタは1.6φの電線を使用した1.4mHです。

2次側の平滑コンデンサも±8,000μFから基板裏に±8,000μFを増量して±16,000μFにしました。

次に周波数特性ですが、指定負荷抵抗を8Ωにししても出力フィルタのコイルをあまり大容量化しない方法を取りました。11.4μH、Cは0.047μF。

結果としてCLKの漏れは大きくなりましたが、F特は十分に伸びたものになりました。

データとしては4Ω負荷も同時に取りましたので、それを次に示します。

次に8Ω負荷時の20Hzと1kHzの歪率を示します。

負荷抵抗を8Ωにした為に見かけの出力は約半分になりましたが、20Hzの最低歪率は約0.008%、1kHzの最低歪率は約0.011%となりました。

☆.試聴テスト

繰り返し、本拠にて試聴テストをしました。

家庭用のアンプとしてもAB級に引けを取らない音質になったと思います。

☆.ここから先は詳論としてページを分けてあります。

ご覧頂ける方はここをクリックして下さい。

このページのトップへ戻りたい方はここをクリックして下さい。

トップページ(目次)へ戻りたい方はここをクリックして下さい。