☆.このページは詳論です。

概論に戻りたい方はここをクリックして下さい。

縮尺されたブロック図や回路図はダウンロードすると全て見る事が出来ます。

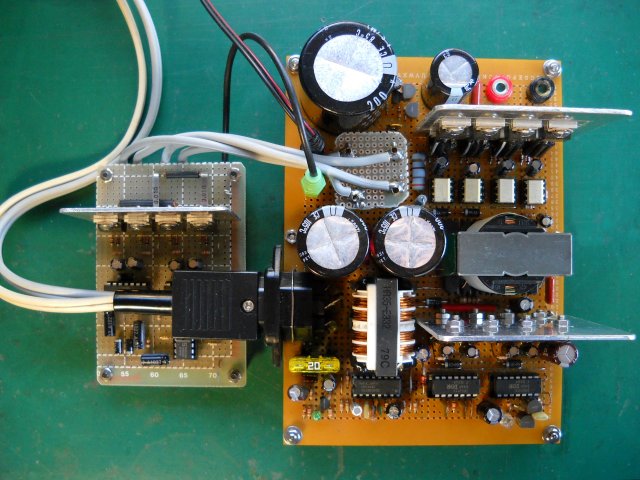

1.ブロック図

☆.ブロック図はFF型とFB型の2つがありますが、先ずFF型からです。

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

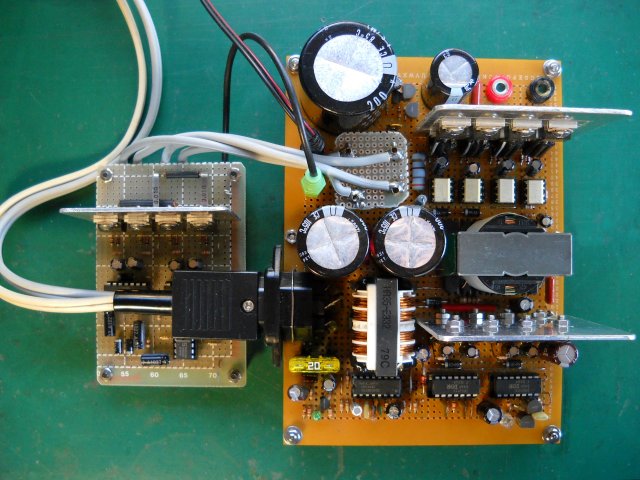

☆.次はFB型です

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

2つのブロック図の違いは左側の正弦波同期整流の部分だけです。

大まかな動作は下記です。

1.AC100V正弦波をFF型またはFB型の正弦波同期整流回路で高効率に整流平滑してDC約135Vの直流を得ます。

2.スイッチング回路によってデッドタイム付きのプッシュプル方形波を作りパルストランスを21kHzで交流駆動します。

3.パルストランスで電圧を変化させた21kHzの方形波の交流を同期整流して直流にします。

2.回路図

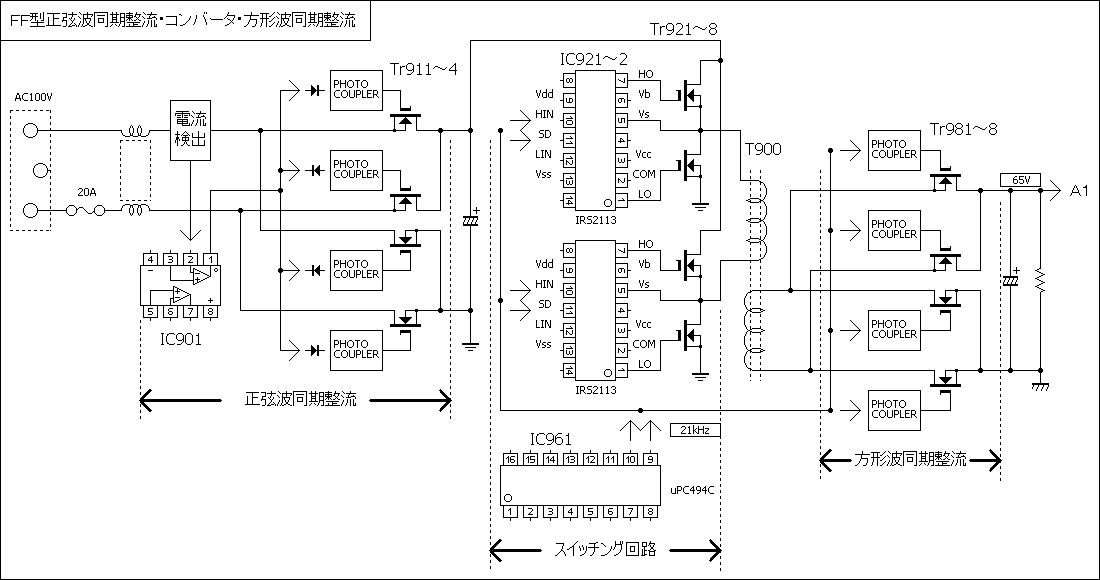

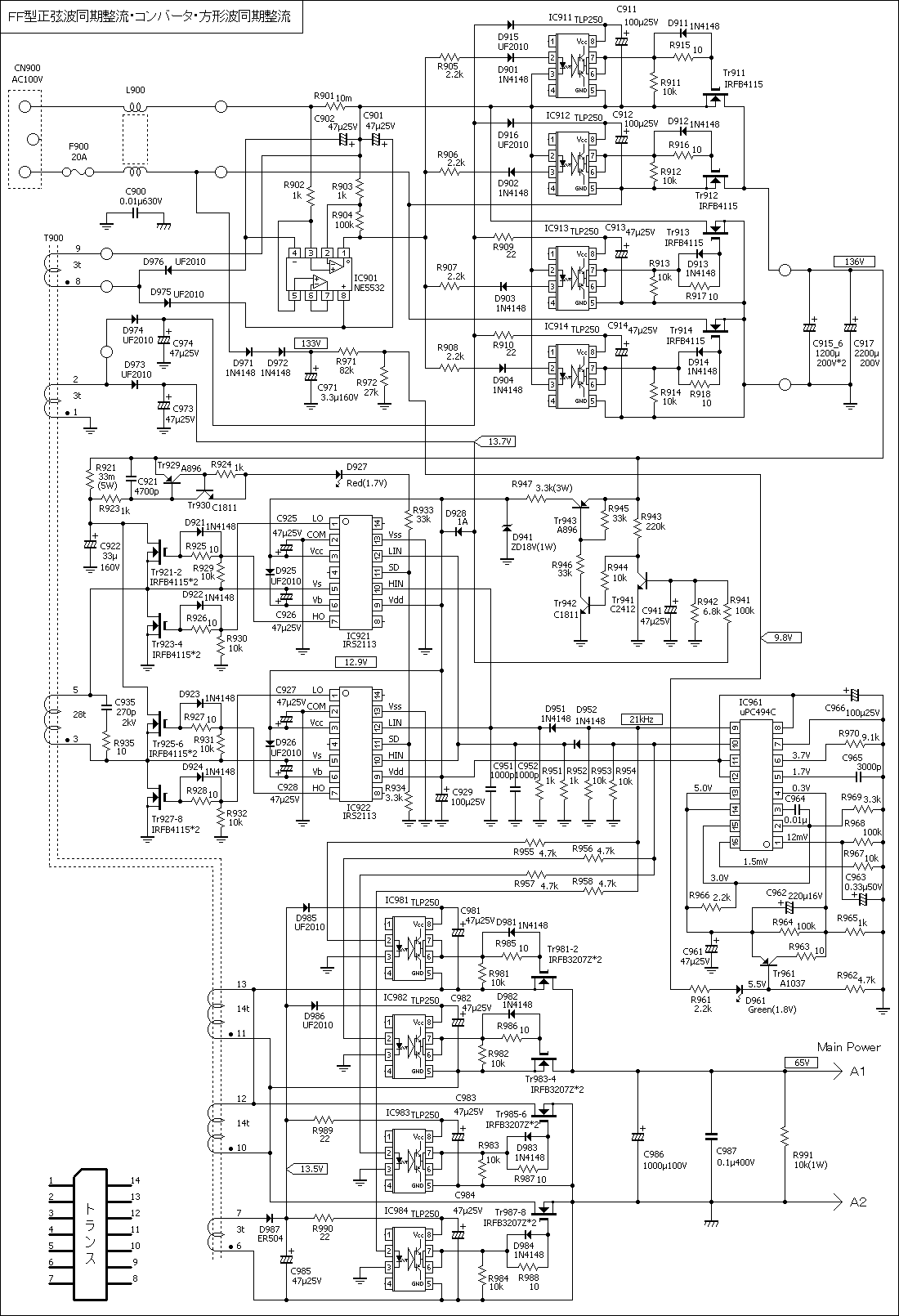

☆.FF型

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

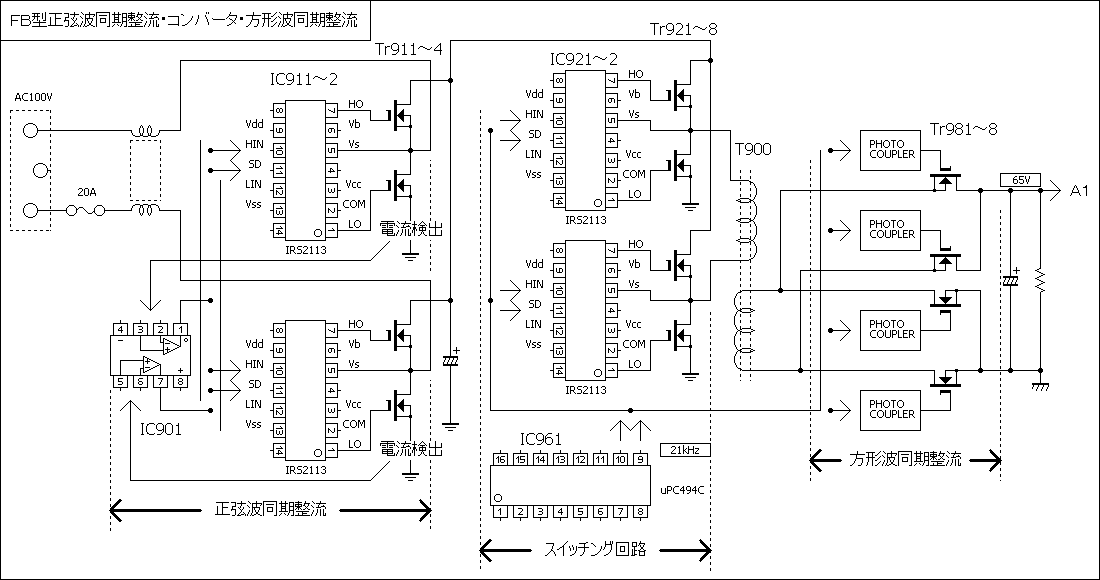

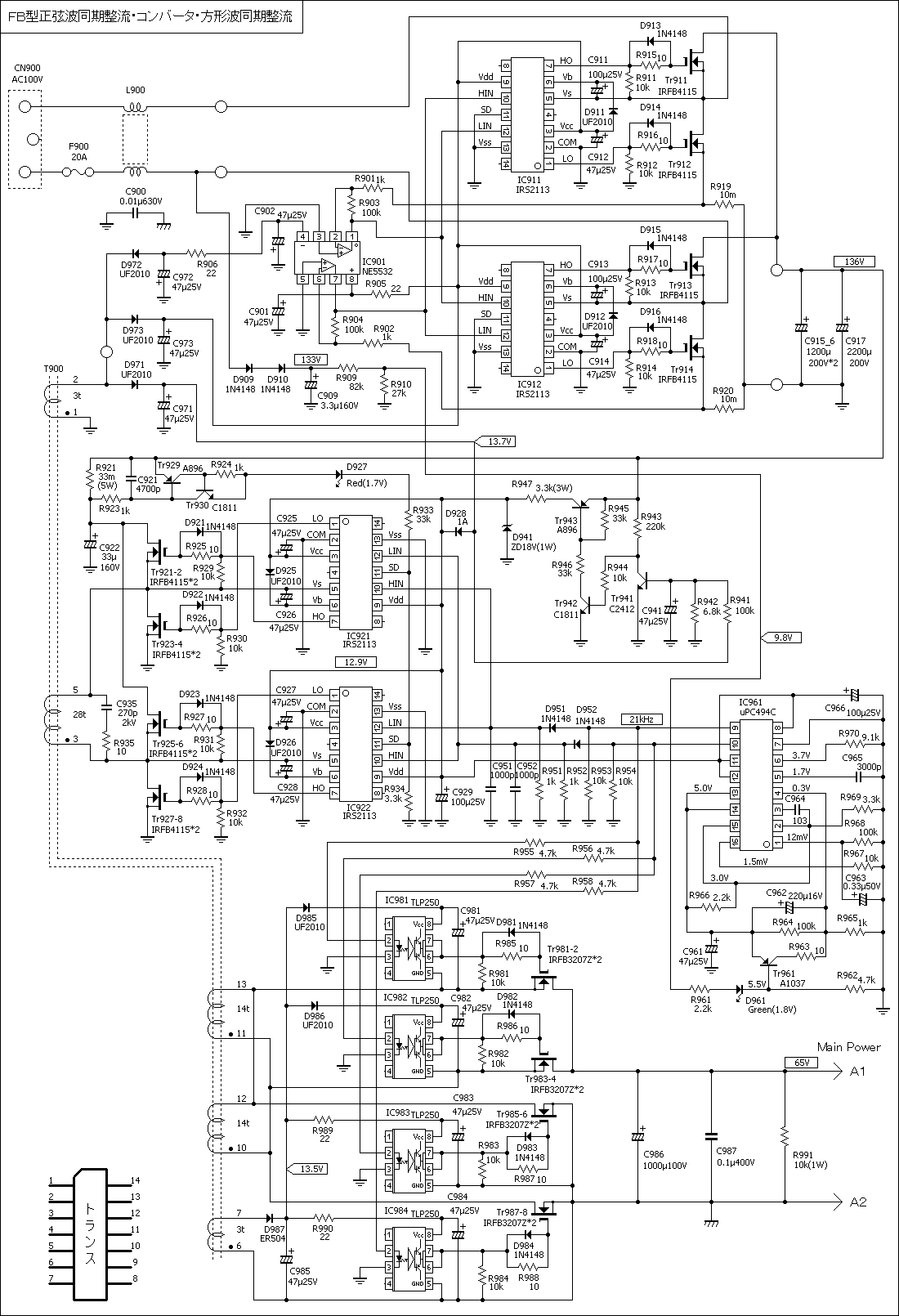

☆.FB型

PDFファイルをご覧になりたい方は をクリックして下さい。

をクリックして下さい。

3.回路説明

☆.2次側方形波の同期整流

1次2次と言う言葉の順序から言えば1次が先なのですが、方形波同期整流の方が皆様にもなじみがあると思うので、こちらを先に述べる事にします。

最近は方形波の同期整流はすでに標準回路化しているようですし、専用のICもたくさん登場しているようですが、今回は従来から標準的に使われているブリッジ整流をMOSETのボディーダイオードに置き替え、これの導通時間の大部分をMOSFET-ONにしようと考えました。

この方法によれば同期整流の為に特別な整流理論を考える必要はなく、ブリッジ整流と言う従来からの整流回路にドライブ回路を附加する事により、整流器で消費していた電力をほとんどなくして効率が向上し、温度が低下する筈です。

さて、方形波を整流する場合は波形のトップは平坦ですから、その期間のほとんど全てに於いて整流電流が流れていると考えられます。

仮に波形平坦期間の中に電流が流れていない期間があって、その時MOSFETがON状態であってもMOSFETの両側の電圧は同じですから差し支えはない訳です。

これが、同期整流の教科書的なものに出てくる2次巻線を延長巻きしたり、3次巻線で同期整流用のMOSFETをドライブする方法です。

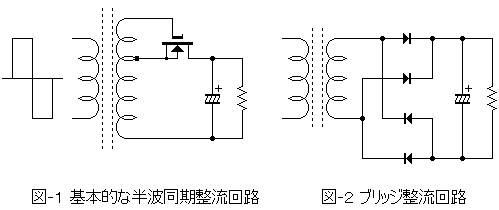

先ず半波同期整流回路と普通のブリッジ整流回路を図示します。

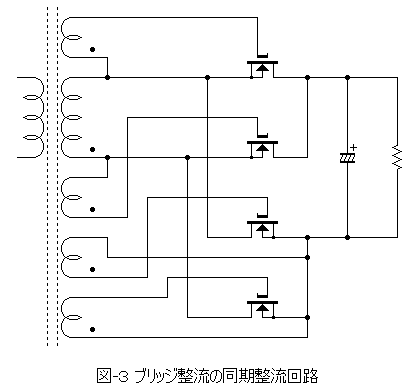

次に図-1の方法を図-2に展開したブリッジ整流の同期整流回路を図示します。

普通は図-3の方法では実用的でないと考え、MOSFETを減らす方法を考えるのでしょう。

しかし、それでは整流器の温度は下がっても全体の効率が上がるかどうか疑問です。同期整流であると言うだけでは意味がありません。

そこで多数の巻線を巻かなくて済む方法として冒頭のブロック図や回路図の方法を考えました。

☆.具体的な方法

先ず、トランスのサブ巻線ではドライブ用の電源だけを作る事とし、両方の回路図中のD985~987、R989~990、およびこれを受けるC981~984によって1つの巻線から4つの電源を形成してMOSFETのドライブ電源としました。

この方法の内、D985とD986によってIC981とIC982の電源を作る方法はブートストラップです。ブートストラップによる電源の作り方はD級アンプのドライブ電源と同じです。

ブートストラップの動作原理については研究テーマ2の詳論で述べていますので、参照してください。

☆.アースの分離

AC100Vを整流平滑した直流から電圧変換をするのは方形波発生回路、ドライブ回路とパルストランスを用いたスイッチング回路で、これらのアースは全て1次側です。

そして、トランスの2次側とは一般的にアースを分離します。

方形波発生回路は1次側なので、光結合によって2次側のMOSFETドライバに接続するのが有利です。

光素子としては高速でMOSFETドライブ能力があるTLP250(東芝)を採用しました。

☆.同期整流ゲートドライブのタイミング

ゲートドライブの方形波はトランスの1次側のMOSFETをドライブする方形波から作ります。

そして、1次側のMOSFETがONした後に2次側のMOSFETがONし、1次側のMOSFETがOFFするより前に2次側のMOSFETをOFFする、つまり、整流開始時と整流終了時はダイオードの状態であるのが良いと考えました。

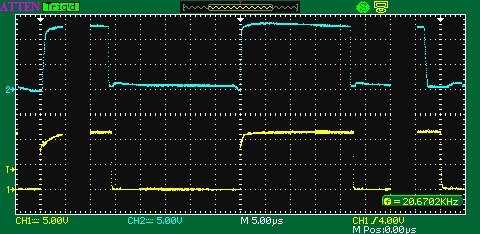

この様子を次のオシロ画面で示します。

画面の上段は2次側MOSFETのゲート、下段は1次側MOSFETのゲートです。

画面の左右両端に横軸を1μSに拡大した立ち上がり部と立ち下り部を入れました。

TLP250には遅延時間があるので同期整流開始はタイミング調整をしなくても自動的にトランス出力よりゲートの方が遅くなります。(0.1μS)

また同期整流終了はTLP250の遅延も見込んで先に終了させます。(0.6μS)

このタイミング調整を回路図中のD951、D952のカソード側のR951、R952、C951、C952によって行っています。

☆.デッドタイム

上記の付加によって1次側のデッドタイムも変動しますので、周辺定数は総合的に検討して決定しました。

最終的には回路図記載の定数でデッドタイムは1.5μSとなっていて、トランスの励磁方向を反転する時の限界である0.9μSに対して0.6μSの余裕をみる事としました。

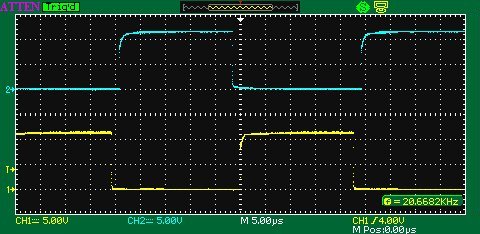

この様子を次のオシロ画面で示します。

上段もOFF、下段もOFFという時間が1.5μSあります。

実は、デッドタイムは少なければ少ないほど効率としては高いのです。

これは効率向上の為には注意する必要があります。

トランスの駆動方式をシングルつまり励磁ON 励磁OFFとするより、プッシュプルつまりプラス励磁 マイナス励磁とする方が効率が高い事は知られています。

ですからプッシュプルにしたのですが、方形波の場合はどうしても反転時にプッシュとプルが共にOFFの時間、つまりデッドタイムが必要となります。

そこで、その限界を求め、それに安全余裕を加えました。

さらに、デッドタイムを1サイクル中のパーセントとして低くするためには駆動周波数を下げるのが良い、ただし、コアと巻き数を勘案して、となります。

その結果として駆動周波数を可聴周波数よりやや高い21kHzにしました。

発振回路用のICは494ファミリーの中でデッドタイムを小さく出来るNECのμPC494Cを採用しました。

☆.1次側AC100Vの同期整流

方形波電源では前記したような固定的なタイミング設定で同期整流が出来ましたが、AC100Vでは使えないのです。

理由は正弦波の場合、通過電力によって整流器の導通角が変わるからです。

また、波形平坦の瞬間はありませんから、導通している時間以外はOFFでなければなりません。

つまり、正弦波の同期整流では導通角と導通タイミングに追従して整流用MOSFETのON時間とタイミングを変化させる必要があります。

☆.整流電流検出と増幅

そこで方法としては整流器であるMOSFETの通過電流を検出して、ある程度以上の電流が流れている間だけMOSFETをONすれば良い筈と考えました。

同時に、小電流では必ずしも同期整流である必要はないと考えました。

電流を検出する方法は検流器などの電流検出素子を使う方法もありますが、電流波形は単純な交流正弦波ではありませんし、回路構成によっては片方向の電流しかない事もあります。

そこで、今回は線路に10mΩを入れ、この両端に発生する電圧を増幅する方法としました。

もちろん、これによる効率低下もありますが、100V1000W中の10mΩは0.1%の効率低下(1W)にとどまるものと言えます。

ただし、仮に最大出力(1000W)の1/10出力(100W)程度から同期整流化しようとすれば、検出電圧は正弦波であれば実効値でわずかに10mVrmsですから40dB増幅しないと1Vrmsにならない訳です。

実際の電流波形は正弦波より尖った波形で、40dB増幅でアンプ出力のピーク値は5V前後となり、100~150Wあたりから同期整流になりました。

しかし、今度は大電流の問題があります。

大電流では過大な電圧、例えば1000Wでは理想アンプならアンプからピーク値約50Vが出力する筈のところ、実際のアンプでは10~15Vで飽和する事になります。

従って出力波形が飽和した後で下がってしまうような事がなく、ゼロが踊らないアンプである必要があります。

この為、アンプには5532と言うオペアンプを採用しました。

また、電流を検出する方法としては整流器の入力側で検出する方法と、整流器の出力側の脈流のところで検出する方法が考えられます。

名称としては整流器の入力側で検出する方法をFF(Feed Forword、前に送る)型、出力側で検出する方法をFB(Feed Back後ろに送るつまり前に戻す)型としました。

☆.FF型

FF型では電流検出とアンプがAC100Vの一方のライン上の1点を基準点として動作します。

この1点の入力側に検出抵抗10mΩを入れて電流を検出し、この1点の上にアンプとアンプ用の独立電源を置きます。

検出出力とアンプ出力は交流出力ですが、ソース電位やタイミングの異なる4つのMOSFETをドライブする為に光結合としました。

つまり、2次側と同じTLP250の採用です。

そして、TLP250のMOSFETドライブ側の電源の作り方は2次側と同じブートストラップです。

ブートストラップ用の元の電源はコンバータ回路をドライブするための電源を用いました。

☆.FB型

FB型では電流検出とアンプは整流器であるMOSFETの出力側、脈流出力のマイナス側に入れました。

従って基準点も直流出力のマイナス側です。

プラス側で検出する事も可能ですが、今回は省略しました。

ブリッジ整流ですから電流検出は両方向の電流を検出する為に2つ必要で、各々がタイミングの異なる出力をします。

これをFF型と同様に40dB増幅しますが、電流検出が2つなのでアンプも2つです。

基準点を脈流出力のマイナス側にしたので光結合の必要はなく、D級アンプ用のドライバでMOSFETをドライブ出来ます。

ドライブ電源の作り方もD級アンプと同じブートストラップです。

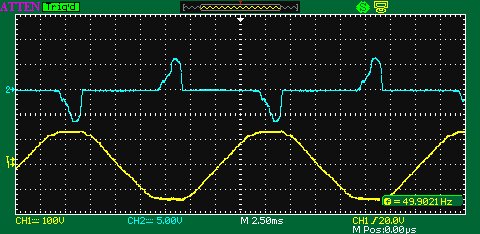

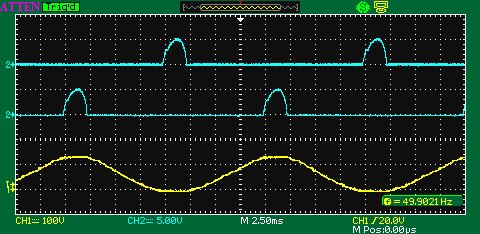

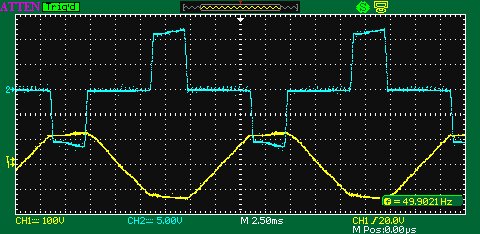

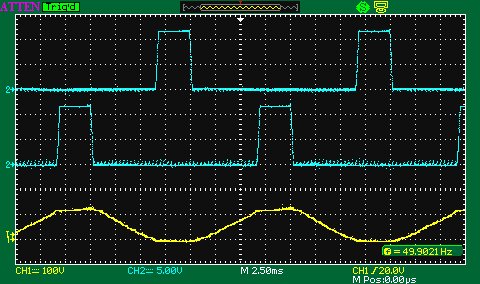

☆.次はFF型とFB型の100W時の検出アンプ出力波形です。

各画面の黄色の大きな正弦波はAC100Vです。

☆.FF型

☆.FB型

FF型では100Wで既に同期整流が始まっているようですが、FB型では始まっていないようです。

FF型の波形がとがっているのがそれを示しています。

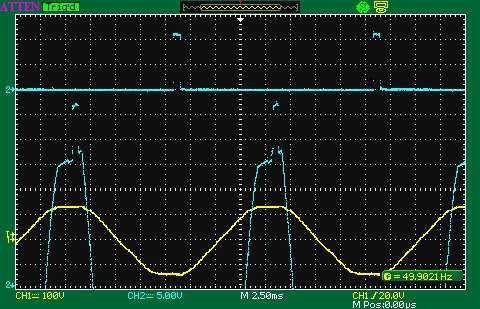

☆.次は1000W時のアンプ出力とAC100Vの波形です。

☆.FF型

☆.FB型

☆.その次にFF型の100W時と1000W時のゲートドライブ波形とAC波形を示します。FB型は省略。

☆.100W時

☆.1000W時

100W時と1000W時を比較すると、ゲートパルスの幅が大きく変化していて、導通角の変化に対応している事が分かります。

また、AC100V波形に載ったゲートパルスは回路図のTr911のゲート波形です。

0~12V程度のゲートパルスがブートストラップによってAC100Vのトップ電圧の上に持ち上げられた事を示しています。

☆.最後に

ここで発表した回路を個人的に利用する事は差し支えありませんが、事業に採用する場合は筆者と契約頂きますよう、お願い致します。

また、この回路は回路素子の保護が十分でない可能性がありますが、それについては採用者の側で十分な吟味と対策をお願いします。

以上

☆.追加論としてトランスの巻線方法について記載しました。

ご覧いただける方はここをクリックして下さい。

このページのトップへ戻りたい方はここをクリックして下さい。

トップページ(目次)へ戻りたい方はここをクリックして下さい。